# Embedded Target for the TI TMS $320C6000^{TM}$ DSP Platform

# For Use with Real-Time Workshop®

- Modeling

- Simulation

- Implementation

#### **How to Contact The MathWorks:**

www.mathworks.com Web

${\tt comp.soft-sys.matlab} \qquad \qquad Newsgroup$

(a)

support@mathworks.com Technical support

${\tt suggest@mathworks.com} \qquad \qquad Product\ enhancement\ suggestions$

bugs@mathworks.com Bug reports

doc@mathworks.com Documentation error reports

service@mathworks.com Order status, license renewals, passcodes info@mathworks.com Sales, pricing, and general information

D

508-647-7000 Phone

508-647-7001 Fax

The MathWorks, Inc. Mail

3 Apple Hill Drive Natick, MA 01760-2098

For contact information about worldwide offices, see the MathWorks Web site.

Embedded Target for the TI TMS320C6000 DSP Platform User's Guide

© COPYRIGHT 2002 - 2004 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

MATLAB, Simulink, Stateflow, Handle Graphics, and Real-Time Workshop are registered trademarks, and TargetBox is a trademark of The MathWorks, Inc.

Other product or brand names are trademarks or registered trademarks of their respective holders.

Printing History: July 2002 Online only Revised for Version 1.0 (Release 13)

January 2003 Online only

September 2003 Online only

June 2004 Online only

Revised for Version 1.1

Revised for Version 2.0 (Release 13SP1+)

Revised for Version 2.1 (Release 14)

August 2004 Online only Revised for Version 2.2

| About the Embedded Target for TI ( | C6000 DSP |

|------------------------------------|-----------|

|                                    |           |

| What Is Embedded Target for the                                                                                                                                                                                                                                                                                                          |                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| TI TMS320C6000 DSP Platform                                                                                                                                                                                                                                                                                                              | . 1-2                                              |

| Suitable Applications                                                                                                                                                                                                                                                                                                                    | . 1-8                                              |

| About Embedded Target for C6000 DSP                                                                                                                                                                                                                                                                                                      | . <b>1-</b> 4                                      |

| Using This Guide                                                                                                                                                                                                                                                                                                                         |                                                    |

| Configuration Information                                                                                                                                                                                                                                                                                                                | . 1-7                                              |

| Getting Started                                                                                                                                                                                                                                                                                                                          | . 1-9                                              |

| Platform Requirements—Hardware and Operating System .                                                                                                                                                                                                                                                                                    | . 1-9                                              |

| Targeting C6000 DSP Hardy                                                                                                                                                                                                                                                                                                                | aro                                                |

|                                                                                                                                                                                                                                                                                                                                          |                                                    |

| Targeting C6000 DSP Hardy  About the Tutorials                                                                                                                                                                                                                                                                                           | . 2-3                                              |

| Targeting C6000 DSP Hardv  About the Tutorials                                                                                                                                                                                                                                                                                           | . <b>2-</b> 3                                      |

| Targeting C6000 DSP Hardy  About the Tutorials                                                                                                                                                                                                                                                                                           | . <b>2-</b> 4                                      |

| Targeting C6000 DSP Hardv  About the Tutorials                                                                                                                                                                                                                                                                                           | . 2-4<br>. 2-4<br>. 2-4                            |

| Targeting C6000 DSP Hardv  About the Tutorials  TI C6000 and Code Composer Studio IDE                                                                                                                                                                                                                                                    | . 2-4<br>. 2-4<br>. 2-6                            |

| Targeting C6000 DSP Hardv  About the Tutorials                                                                                                                                                                                                                                                                                           | . 2-4<br>. 2-4<br>. 2-6<br>2-10<br>2-11            |

| Targeting C6000 DSP Hardv  About the Tutorials                                                                                                                                                                                                                                                                                           | . 2-4<br>. 2-4<br>. 2-6<br>. 2-10<br>2-19<br>2-25  |

| Targeting C6000 DSP Hardv  About the Tutorials                                                                                                                                                                                                                                                                                           | 2-4<br>2-4<br>2-10<br>2-15<br>2-25<br>2-28         |

| About the Tutorials                                                                                                                                                                                                                                                                                                                      | 2-4<br>2-4<br>2-10<br>2-19<br>2-25<br>2-28<br>2-28 |

| Targeting C6000 DSP Hardv  About the Tutorials  TI C6000 and Code Composer Studio IDE  Supported Boards and Simulators  Typical Hardware Setup for Developing Models  Using the C6000lib Blockset  Configuring ADC Blocks  Configuring DAC Blocks  Configuring LED Blocks  Using the Overrun Indicator Feature                           | . 2-3<br>. 2-4<br>. 2-4<br>. 2-6                   |

| Targeting C6000 DSP Hardv  About the Tutorials  TI C6000 and Code Composer Studio IDE  Supported Boards and Simulators  Typical Hardware Setup for Developing Models  Using the C6000lib Blockset  Configuring ADC Blocks  Configuring DAC Blocks  Configuring LED Blocks  Using the Overrun Indicator Feature  Configuring Reset Blocks | 2-4<br>2-4<br>2-10<br>2-19<br>2-25<br>2-28<br>2-29 |

| Using Logging in Your DSP Applications              | 2-35  |

|-----------------------------------------------------|-------|

| Generating Code from Real-Time Models               |       |

|                                                     |       |

| Setting Real-Time Workshop Build Options for        |       |

| C6000 Hardware                                      | 2-37  |

| Real-Time Workshop Options for C6000 Hardware       | 2-37  |

| Target Configuration Options                        | 2-39  |

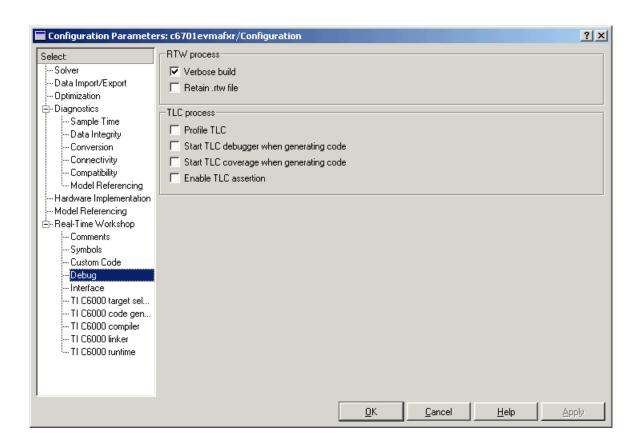

| Target Language Compiler Debugging Options          | 2-42  |

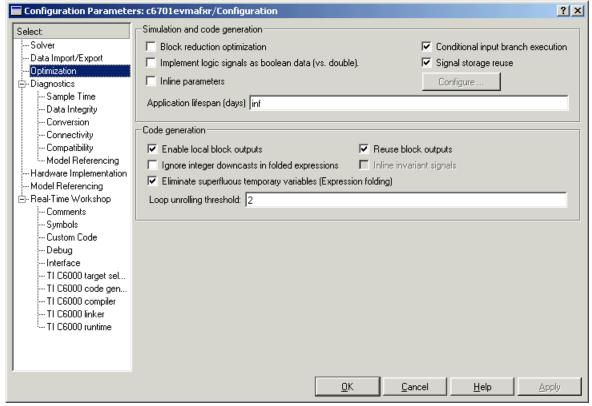

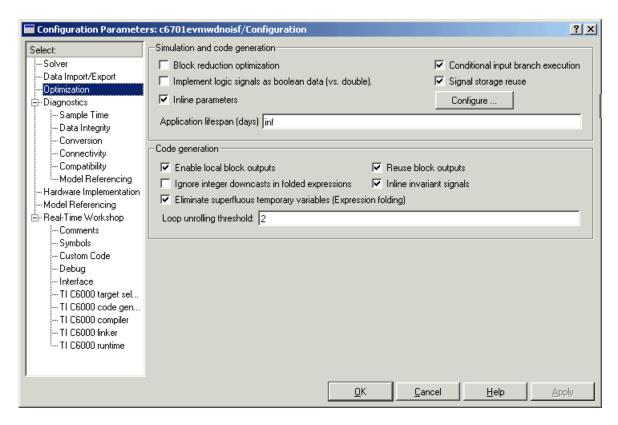

| General Code Generation Category Options            | 2-43  |

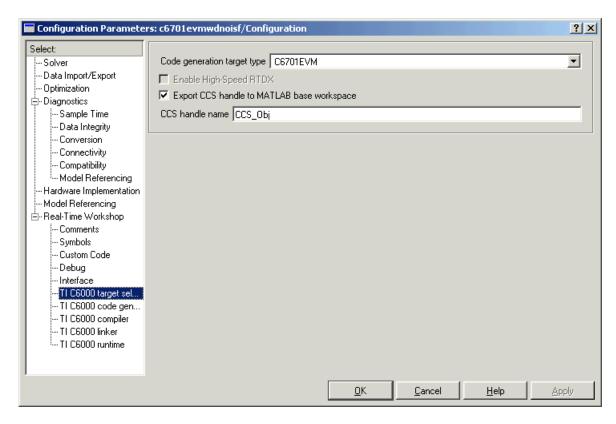

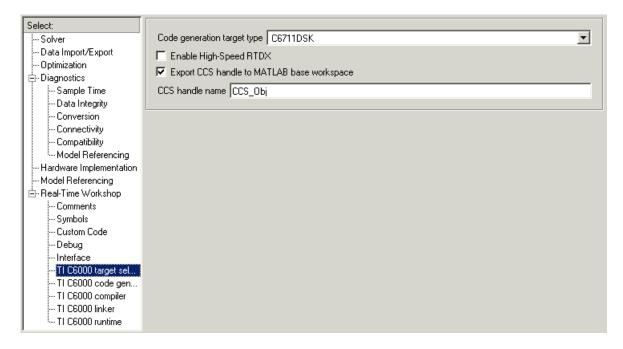

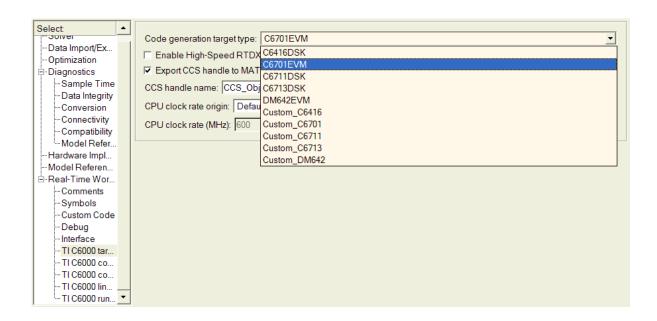

| TI C6000 Target Selection                           | 2-44  |

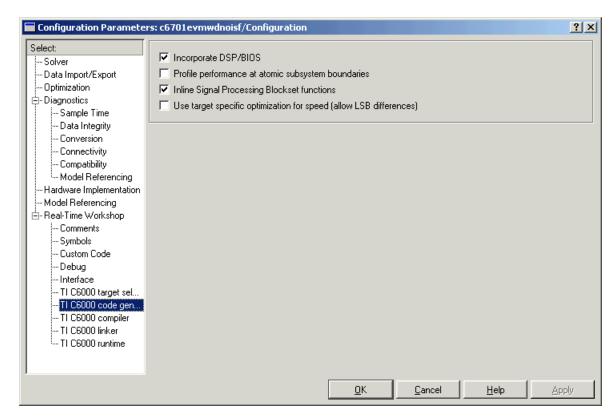

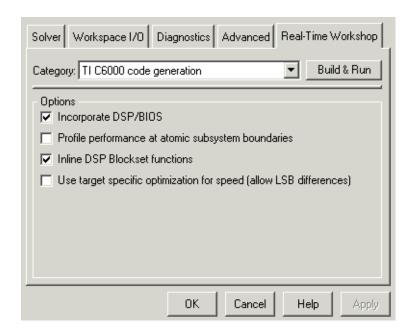

| TI C6000 Code Generation Options                    | 2-47  |

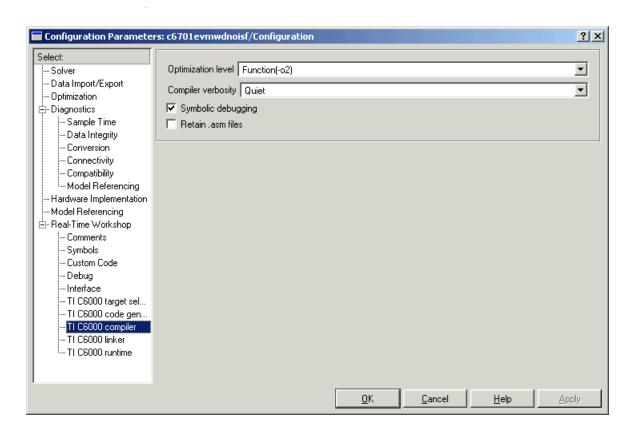

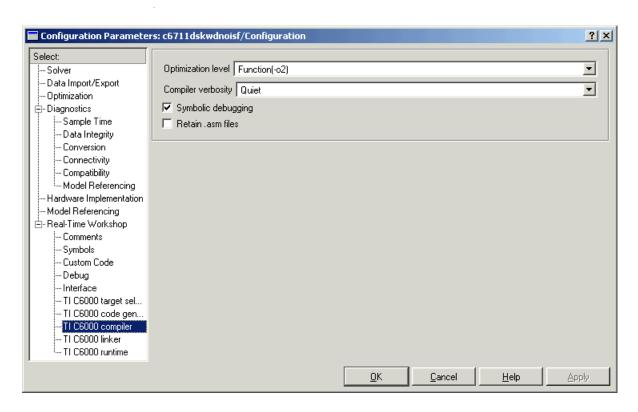

| TI C6000 Compiler Options                           | 2-49  |

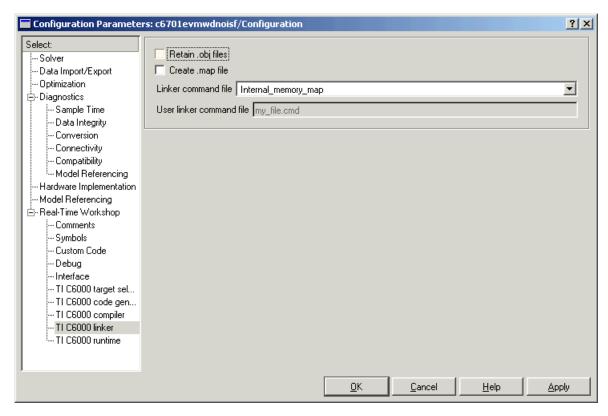

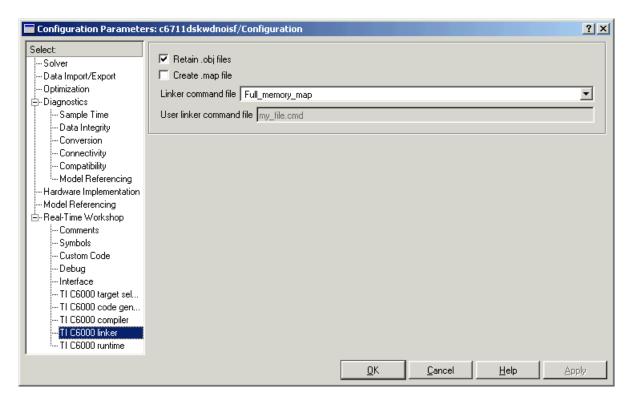

| TI C6000 Linker Options                             | 2-51  |

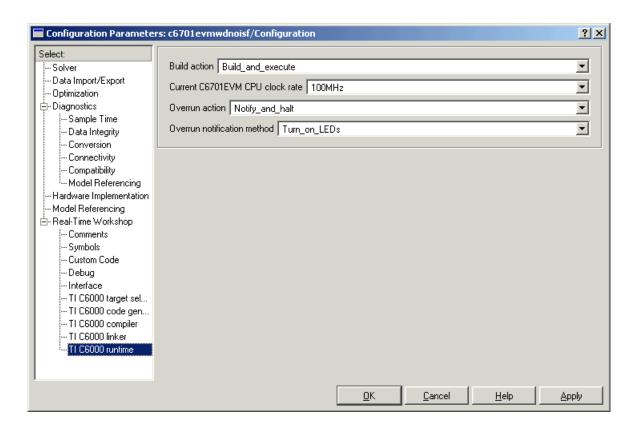

| TI C6000 Run-Time Options                           | 2-56  |

| Embedded Target for TI C6000 DSP                    |       |

| Default Project Configuration—custom_MW             | 2-61  |

| Targeting Your C6701 EVM and Other Hardware         | 2-63  |

| Configuring Your C6701 EVM                          |       |

| Confirming Your C6701 EVM Installation              |       |

| Testing Your C6701 EVM                              |       |

| Creating Your Simulink Model for Targeting          |       |

| C6701 EVM Tutorial 2-1—Single Rate Application      | 2-74  |

| Specifying Configuration Parameters for Your Model  |       |

| Specifying Configuration Farameters for Tour Model  | 4-19  |

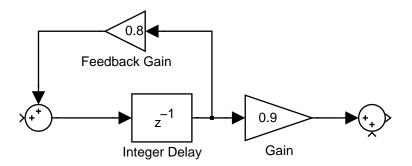

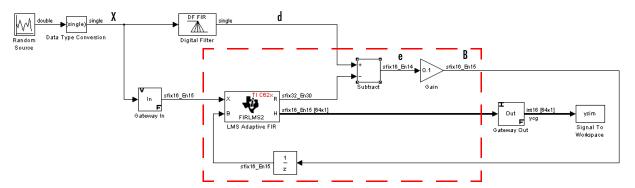

| C6701 EVM Tutorial 2-2—A Multistage Application     | 2-82  |

| Targeting Your C6711 DSK and Other Hardware         | 2-97  |

| Configuring Your C6711 DSK                          | 2-97  |

| Confirming Your C6711 DSK Installation              | 2-97  |

| Testing Your C6711 DSK                              | 2-98  |

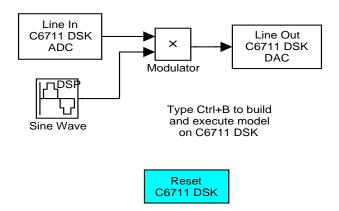

| Running Models on Your C6711 DSK                    | 2-102 |

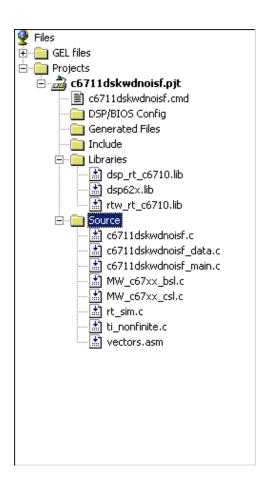

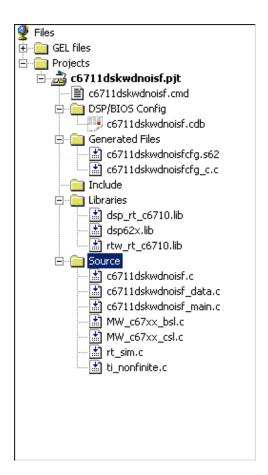

| C6711 DSK Tutorial 2-3—Single Rate Application      | 2-105 |

| Configuring Configuration Parameters for Your Model |       |

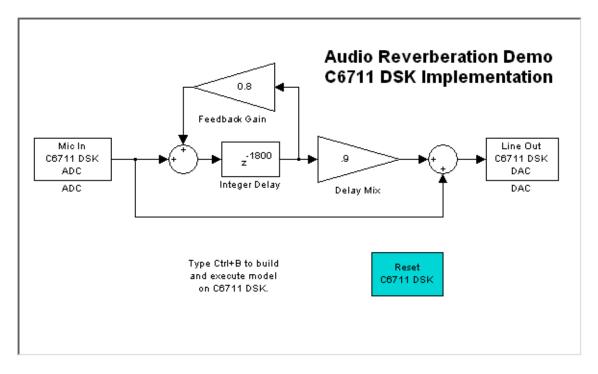

| C6711 DSK Tutorial 2-4—A More Complex Application   | 2-114 |

|        | ut Building                                                        |    |

|--------|--------------------------------------------------------------------|----|

| Targe  | ting Custom Hardware                                               | 2- |

|        | Embedded Target for TI C6000 DSP with Time Workshop Embedded Coder | 2- |

|        | Targeting with DSP/BIOS™ Opti                                      | o  |

| Introd | ucing DSP/BIOS <sup>TM</sup>                                       |    |

|        | IOS and Targeting Your TI C6000™ DSP                               |    |

|        | /BIOS Configuration File                                           |    |

|        | nory Mapping                                                       |    |

|        | dware Interrupt Vector Table                                       |    |

| Link   | er Command File                                                    | •  |

|        | Generation with DSP/BIOS                                           |    |

| Gen    | erated Code Without and With DSP/BIOS                              |    |

| Profil | ng Generated Code                                                  | •  |

| Prof   | iling Subsystems                                                   | •  |

|        | iling Multitasking Systems                                         |    |

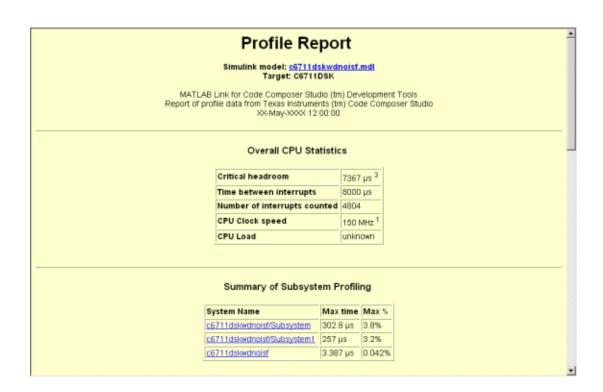

|        | Profiling Report                                                   |    |

|        | rrupts and Profiling                                               |    |

|        | ling Your Profile Report                                           |    |

|        | nitions of Report Entries                                          |    |

| Prof   | iling Your Generated Code                                          |    |

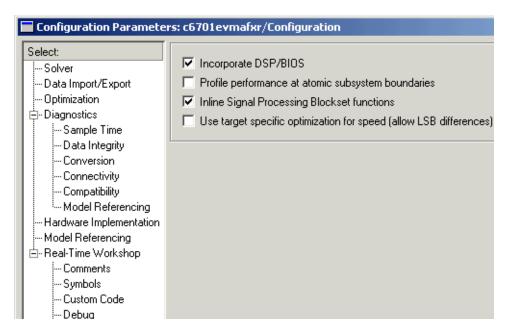

|        | nable Profiling for Your Generated Code                            |    |

|        |                                                                    | •  |

| Λ | ı |

|---|---|

|   | ۰ |

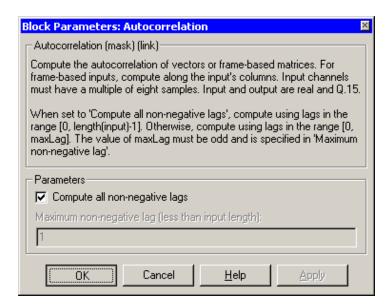

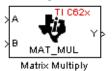

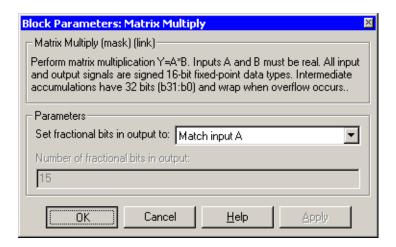

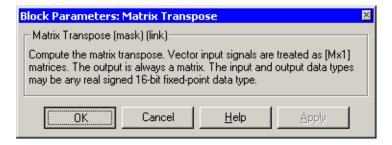

|   | About the C62x and C64x DSP Libraries                  |             |

|---|--------------------------------------------------------|-------------|

|   | Characteristics Common to C62x and C64x Library Blocks | <b>4-</b> 3 |

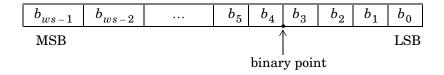

|   | Fixed-Point Numbers                                    |             |

|   | Signed Fixed-Point Numbers                             | 4-4         |

|   | Q Format Notation                                      | 4-5         |

|   | Building Models                                        | <b>4-8</b>  |

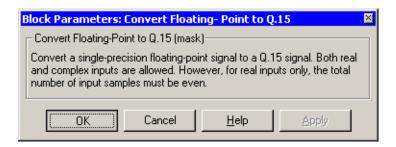

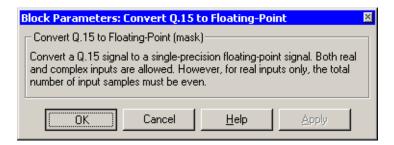

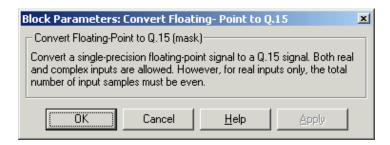

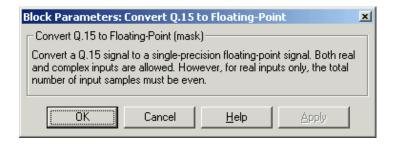

|   | Converting Data Types                                  | 4-8         |

|   | Using Sources and Sinks                                | 4-9         |

|   | Choosing Blocks to Optimize Code                       |             |

|   |                                                        |             |

|   | Block Reference                                        | ce          |

| 5 |                                                        |             |

|   | I                                                      |             |

|   | Using the Embedded Target for                          |             |

|   | C6000 DSP Block Reference                              | <b>5</b> -2 |

|   |                                                        |             |

|   | Blocks—Categorical List                                | <b>5-</b> 3 |

|   | Embedded Target for C6000 DSP Blocks                   |             |

|   | in Library c6701evmlib                                 | <b>5-</b> 3 |

|   | Embedded Target for C6000 DSP Blocks                   |             |

|   | in Library c6711dsklib                                 | <b>5</b> -3 |

|   | Embedded Target for C6000 DSP Blocks                   |             |

|   | in Library rtdxblocks                                  | <b>5-4</b>  |

|   | Embedded Target for C6000 DSP Blocks                   |             |

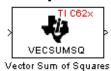

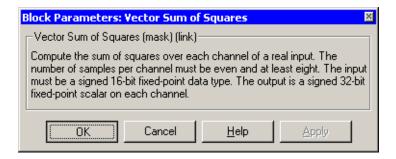

|   | in the C62x DSP Library                                | <b>5-4</b>  |

|   | Embedded Target for C6000 DSP Blocks                   |             |

|   | in the C64x DSP Library                                | 5-7         |

|   |                                                        |             |

|   | Embedded Target for TI C6000 DSP Blocks                |             |

|   | in the C6416 DSP Library                               | <b>5-</b> 9 |

|   | in the C6416 DSP Library                               |             |

|   | in the C6416 DSP Library                               |             |

|          | in the DM642 EVM Library <b>5-10</b>                            | )      |

|----------|-----------------------------------------------------------------|--------|

|          | Embedded Target for TI C6000 DSP Blocks                         |        |

|          | in the C6000 DSP Core Support Library 5-11                      | L      |

|          | Embedded Target for TI C6000 DSP Blocks                         |        |

|          | in the TMDX326040A DSP Support Library 5-11                     | Ĺ      |

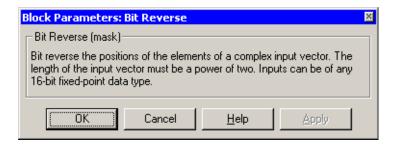

|          | Blocks — Alphabetical List                                      | 2      |

|          |                                                                 |        |

|          |                                                                 |        |

|          | D. C                                                            |        |

|          | Reference — Supported Hardware                                  | : _    |

| A        | Reference — Supported Hardware                                  | :      |

| A        |                                                                 | _      |

| A        | Reference — Supported Hardware Supported Hardware For Targeting | _      |

| A        |                                                                 | 2      |

| A        | Supported Hardware For Targeting A-2                            | 2      |

| <b>A</b> | Supported Hardware For Targeting                                | 2<br>1 |

# About the Embedded Target for TI C6000 DSP

What Is Embedded Target for the TI TMS320C6000 DSP Platform (p. 1-2)

About Embedded Target for C6000 DSP (p. 1-4)

Using This Guide (p. 1-5)

Configuration Information (p. 1-7)

Getting Started (p. 1-9)

Introduces the Embedded Target for TI C6000 DSP, some of the features and supported hardware

Presents an overview of the capabilities of the Embedded Target for TI C6000 DSP

Introduces the organization of the User's Guide and provides summaries of each section

Describes how to determine if you have installed Embedded Target for TI C6000 DSP

Talks about the software and hardware required to use the Embedded Target for TI C6000 DSP, from both The MathWorks and from Texas Instruments

# What Is Embedded Target for the TI TMS320C6000 DSP Platform

Embedded Target for the TI TMS320C6000 DSP Platform integrates Simulink and MATLAB with Texas Instruments express DSP tools. The software collection lets you develop and validate digital signal processing designs from concept through code. The Embedded Target for TI C6000 DSP consists of the TI C6000 target that automates rapid prototyping on your C6000 hardware targets. The target uses C code generated by Real-Time Workshop and your TI development tools to build an executable file for your targeted processor. The Real-Time Workshop build process loads the targeted machine code to your board and runs the executable file on the digital signal processor.

Using the Embedded Target for TI C6000 DSP and Real-Time Workshop, you can create executable code for the following boards:

- C6416 DSP Starter Kit from Texas Instruments

- C6701 Evaluation Module from Texas Instruments, revision 1 or later

- C6711 DSP Starter Kit from Texas Instruments

- C6713 DSP Starter Kit from Texas Instruments

- TMDX326040A Daughter card for the C6711 DSK. Also known as the PCM3003 Audio Daughter Card.

Additionally, one of the Real-Time Workshop build options builds a Code Composer Studio $^{\text{\tiny TM}}$  project from the C code generated by Real-Time Workshop.

All the features provided by Code Composer Studio (CCS), such as tools for editing, building, debugging, code profiling, and project management, work to help you develop applications using MATLAB, Simulink, Real-Time Workshop, and your supported hardware. When you use this target, the build process creates a new project in Code Composer Studio and populates the project with the files the project requires.

As long as your TI hardware, whether built by TI or custom, supports communications over JTAG and RTDX, you can use the Embedded Target for TI C6000 DSP with your hardware, enabling you to maximize the results of your development time and effort.

This chapter provides sections that describe the following:

- Some of the digital signal processing applications you can develop with Embedded Target for TI C6000 DSP, in the section "Suitable Applications" on page 1-3

- Prerequisites for using Embedded Target for TI C6000 DSP, in the section "Platform Requirements—Hardware and Operating System" on page 1-9

## **Suitable Applications**

The Embedded Target for TI C6000 DSP enables you to develop digital signal processing applications that have any of the following characteristics:

- Single rate

- Multirate

- Multistage

- Adaptive

- Frame based

- Fixed point when you use the C62x or C64x blocks with C64xx and C67xx targets.

Your supported boards, and the Embedded Target for TI C6000 DSP, cover a range of standard input sampling frequencies from 5.5 KHz to 48 KHz or more. The specific supported input range depends on the board you own.

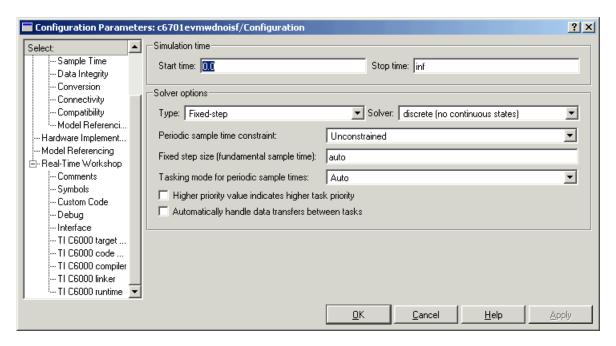

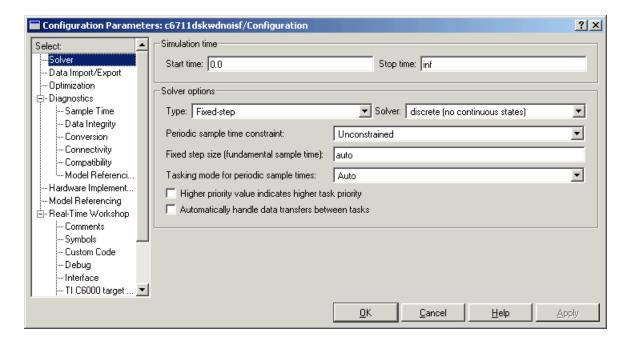

For any model to work in the targetting environment, you must select the discrete-time solver in the Simulink **Solver** options. Targetting does not work with continuous time solvers.

# **About Embedded Target for C6000 DSP**

Embedded Target for TI C6000 DSP lets you use Simulink® to model digital signal processing algorithms from blocks in the DSP Blockset, and then use Real-Time Workshop® to generate (or build) ANSI C code targeted to the Texas Instruments DSP development boards or Texas Instruments Code Composer Studio  $^{\mathsf{IM}}$  Integrated Development Environment (CCS IDE). The Embedded Target for TI C6000 DSP takes the generated C code and uses Texas Instruments (TI) tools to build specific machine code depending on the TI board you use. The build process downloads the targeted machine code to the selected hardware and runs the executable on the digital signal processor. After downloading the code to the board, your digital signal processing (DSP) application runs automatically on your target.

## **Using This Guide**

This section provides some guidance for using this book to learn more about the Embedded Target for TI C6000 DSP.

## **Expected Background**

This document introduces you to using Embedded Target for C6000 DSPs with Real-Time Workshop to develop digital signal processing applications for the Texas Instruments CC6000 family of DSP development hardware, such as the TI TMS320C6701 Evaluation Module. To get the most out of this manual, you should be familiar with MATLAB and its associated programs, such as DSP Blockset and Simulink. We do not discuss details of digital signal processor operations and applications, except to introduce concepts related to using the C6701 EVM or C6711 DSK. For more information about digital signal processing, you may find one or more of the following books helpful:

- McClellan, J. H., R. W. Schafer, and M. A. Yoder, DSP First: A Multimedia Approach, Prentice Hall, 1998.

- Lapsley, P., J. Bier, A. Sholam, and E. A. Lee, *DSP Processor Fundamentals Architectures and Features*, IEEE Press, 1997.

- Oppenheim, A.V., R. W. Schafer, Discrete-Time Signal Processing, Prentice-Hall, 1989.

- Mitra, S. K., Digital Signal Processing—A Computer-Based Approach, The McGraw-Hill Companies, Inc, 1998.

- Steiglitz, K, A Digital Signal Processing Primer, Addison-Wesley Publishing Company, 1996.

For information about Code Composer Studio and Real-Time Data Exchange<sup>TM</sup> (RTDX<sup>TM</sup>), refer to your Texas Instruments documentation for each product. Refer to the documentation for your TI boards for information about setting them up and using them.

#### If You Are a New User

New users should read Chapter 1, "About the Embedded Target for TI C6000 DSP." This introduces the Embedded Target for TI C6000 DSP environment — the required software and hardware, installation requirements, and the board configuration settings that you need. You will find descriptions of the blocks associated with the targeting software, and an introduction to the range of

digital signal processing applications that Embedded Target for C6000 DSPs supports.

#### If You Are an Experienced User

All users should read Chapter 2, "Targeting C6000 DSP Hardware" for information and examples about using the new blocks and build software to target both your C6701 EVM or your C6711 DSK. Two example models introduce the targeting software and build files, and give you an idea of the range of applications supported by Embedded Target for C6000 DSPs. Visit "Confirming Your C6701 EVM Installation" on page 2-66, to confirm that you installed and configured your C6701 EVM board to meet the needs of Embedded Target for C6000 DSPs. For C6711 DSK users, refer to "Configuring Your C6711 DSK" on page 2-97 for more information about installing and using your C6711 DSK.

# **Configuration Information**

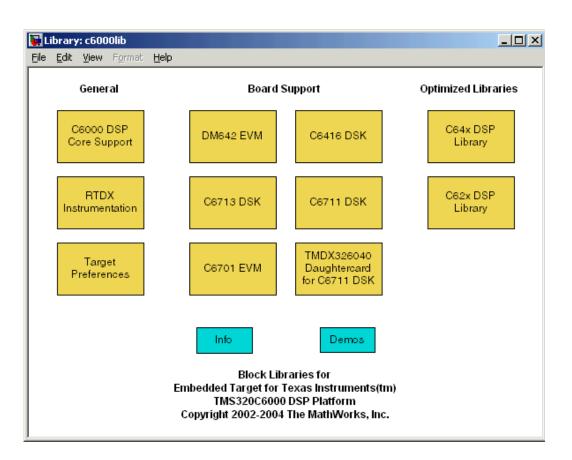

To determine whether the Embedded Target for TI C6000 DSP is installed on your system, type this command at the MATLAB prompt.

c60001ib

When you enter this command, MATLAB displays the C6000 block library containing the following libraries that comprise the C6000 library:

- C6000 DSP Core Support

- C62x DSP Library

- C64x DSP Library

- C6416 DSK Board Support

- C6701 EVM Board Support

- C6711 DSK Board Support

- C6713 DSK Board Support

- RTDX Instrumentation

- TMDX326040 Daughtercard Support

If you do not see the listed libraries, or MATLAB does not recognize the command, install the Embedded Target for TI C6000 DSP. Without the software, you cannot use Simulink and Real-Time Workshop to develop applications targeted to the TI boards.

**Note** For up-to-date information about system requirements, refer to the system requirements page, available in the products area at the MathWorks Web site (http://www.mathworks.com).

To verify that CCS is installed on your machine, enter

ccsboardinfo

at the MATLAB command line. With CCS installed and configured, MATLAB returns information about the boards that CCS recognizes on your machine, in a form similar to the following listing.

| Board | Board                          | Proc | Processor |

|-------|--------------------------------|------|-----------|

|       | Processor                      |      |           |

| Num   | Name                           | Num  | Name      |

|       | Туре                           |      |           |

|       |                                |      |           |

|       |                                |      |           |

| 1     | C6xxx Simulator (Texas Instrum | 0    | 6701      |

|       | TMS320C6701                    |      |           |

| 0     | C6x11 DSK (Texas Instruments)  | 0    | CPU       |

|       | TMS320C6x1x                    |      |           |

If MATLAB does not return information about any boards, revisit your  ${\rm CCS}$  installation and setup in your  ${\rm CCS}$  documentation.

As a final test, launch CCS to ensure that it starts up successfully. For the Embedded Target for TI C6000 DSP to operate with CCS, the CCS IDE must be able to run on its own.

# **Getting Started**

This section describes the hardware and software you need to run the Embedded Target for TI C6000 DSP on your Microsoft Windows PC.

Embedded Target for TI C6000 DSP runs on Microsoft Windows NT 4.0 Workstation and Server, Windows 2000, and Windows XP platforms.

# Platform Requirements—Hardware and Operating System

To run the Embedded Target for TI C6000 DSP, your host PC must meet the following hardware configuration:

- Intel Pentium or Intel Pentium processor compatible PC

- 64 MB RAM (128 MB recommended)

- 20 MB hard disk space available after installing MATLAB

- Color monitor

- One full-length peripheral component interface (PCI) slot available to use the C6701 EVM internally in your PC

- CD-ROM drive

- Microsoft Windows NT 4.0 Server or Workstation, Windows 2000, or Windows XP. Note that the C6416 DSK and C6713 DSK do not work on Microsoft Windows NT platforms.

You may need additional hardware, such as signal sources and generators, microphones, oscilloscopes or signal display systems, and assorted audio cables to test and evaluate your digital signal processing application on your hardware.

Refer to your documentation from The MathWorks for more information on installing the software required to support Embedded Target for TI C6000 DSP, as shown in Table 1-1. In all cases, Embedded Target for TI C6000 DSP requires that you install the latest versions of the required software.

Table 1-1: Prerequisites for Using Embedded Target for TI C6000 DSP Software for Targeting

| Installed Product                                                  | Additional Information                                                                                                                                                                             |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MATLAB                                                             | Core software from The MathWorks                                                                                                                                                                   |

| Link for Code<br>Composer Studio <sup>™</sup><br>Development Tools | Software to enable communications between MATLAB and the Code Composer Studio development environment. Required for the Embedded Target for TI C6000 DSP to work in code generation and targeting. |

| Real-Time Workshop                                                 | Software used to generate C code from Simulink models                                                                                                                                              |

| Simulink                                                           | Software package for modeling, simulating, and analyzing dynamic systems                                                                                                                           |

| Signal Processing<br>Toolbox                                       | Software package for analyzing signals, processing signals, and developing algorithms                                                                                                              |

| DSP Blockset                                                       | Block libraries used by Simulink                                                                                                                                                                   |

For information about the software required to use the Link for Code Composer Studio Development Tools, refer to the Products area of the MathWorks Web site—http://www.mathworks.com.

#### Texas Instruments Software

In addition to the required software from The MathWorks, Embedded Target for TI C6000 DSP requires that you install the Texas Instruments development tools and software listed in the following table. Installing Code Composer Studio IDE for the C6000 series, the latest version, installs the software shown.

Table 1-2: Required TI Software for Targeting Your TI C6000 Hardware

| Installed Product                | Additional Information                                                                                                                                                |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Assembler                        | Creates object code (.obj) for C6000 boards from assembly code.                                                                                                       |

| Compiler                         | Compiles C code from the blocks in<br>Simulink models into object code (.obj). As<br>a byproduct of the compilation process, you<br>get assembly code (.asm) as well. |

| Linker                           | Combines various input files, such as object files and libraries.                                                                                                     |

| Code Composer Studio             | Texas Instruments integrated development environment (IDE) that provides code debugging and development tools.                                                        |

| TI C6000 miscellaneous utilities | Various tools for developing applications for<br>the C6000 digital signal processor family.                                                                           |

| Code Composer Setup<br>Utility   | Program you use to configure your CCS installation by selecting your target boards or simulator.                                                                      |

In addition to the TI software, you need one or more of the following in any combination:

- One or more Texas Instruments TMS320C6416 DSP Starter Kits

- One or more Texas Instruments TMS320C6701 Evaluation Modules

- One or more TMS320C6711 DSP Starter Kits

- One or more TMS320C6713 DSP Starter Kits

- One or more TMDX326040A Daughter Cards for the C6711 DSK, used with the DSK. This daughter card is also known as the PCM3003 Audio Daughter Card

- One or more configured simulators for any supported digital signal processors

For up-to-date information about the software from The MathWorks you need to use the Embedded Target for TI C6000 DSP, refer to the MathWorks Web site—http://www.mathworks.com. Check the Product area for the Embedded Target for the TI TMS320C6000 DSP Platform.

# Targeting C6000 DSP Hardware

TI C6000 and Code Composer Studio IDE (p. 2-4)

Using the C6000lib Blockset (p. 2-10)

Setting Real-Time Workshop Build Options for C6000 Hardware (p. 2-37)

Targeting Your C6701 EVM and Other Hardware (p. 2-63)

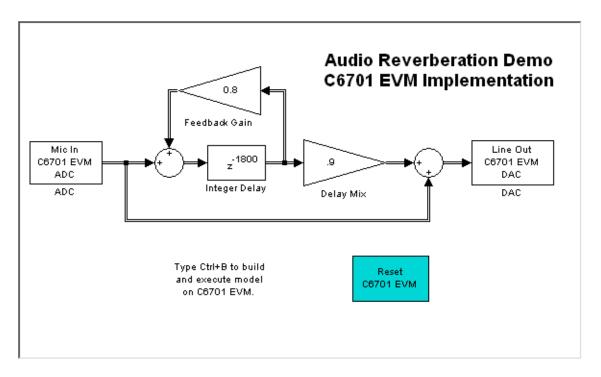

C6701 EVM Tutorial 2-1—Single Rate Application (p. 2-74)

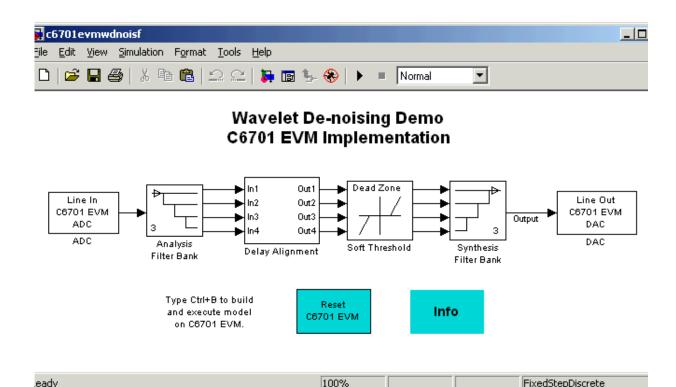

C6701 EVM Tutorial 2-2—A Multistage Application (p. 2-82)

Targeting Your C6711 DSK and Other Hardware (p. 2-97)

C6711 DSK Tutorial 2-3—Single Rate Application (p. 2-105)

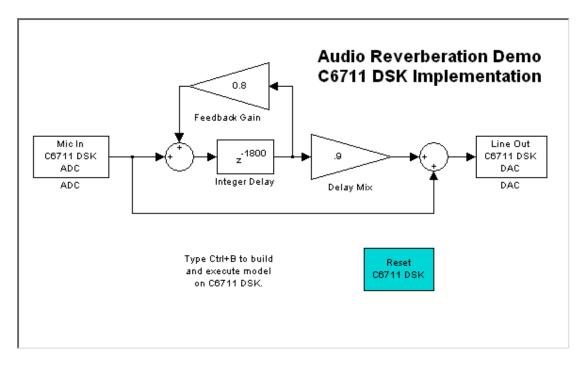

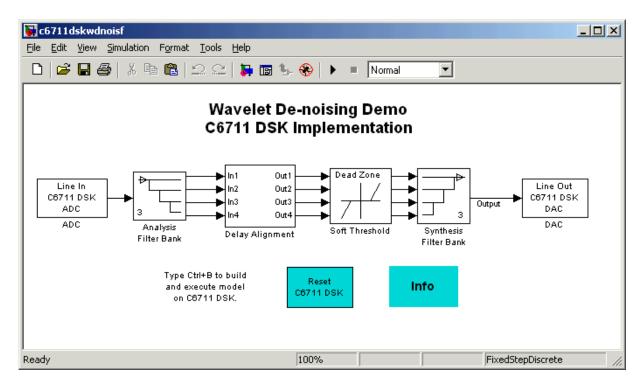

C6711 DSK Tutorial 2-4—A More Complex Application (p. 2-114) Discusses the blocks provided by the Embedded Target for TI C6000 DSP for developing models for TI C6000 $^{\text{TM}}$  DSP platforms. Also lists the supported hardware.

Describes the contents of the C6000lib blockset—what blocks are included and where, and briefly describes how to configure the target-specific blocks generally.

Provides the details on setting the Real-Time Workshop options when you generate code from your Simulink models to TI hardware.

If you are targeting a C6701 EVM, this section details specific information about using the target.

Takes you through the process of creating models in Simulink and generating code for your targets. Uses the 6701 EVM as the example board.

Using a more complex model than the previous tutorial, this exercise walks you through code generation for a multistage model.

If you are targeting a C6711 DSK, this section details specific information about using the target, although the process shown applies to other targets equally.

Takes you through the process of creating models in Simulink and generating code for the C6711 DSK

Using a more complex model than the previous C6711 DSK tutorial, this exercise walks you through code generation for a multistage model

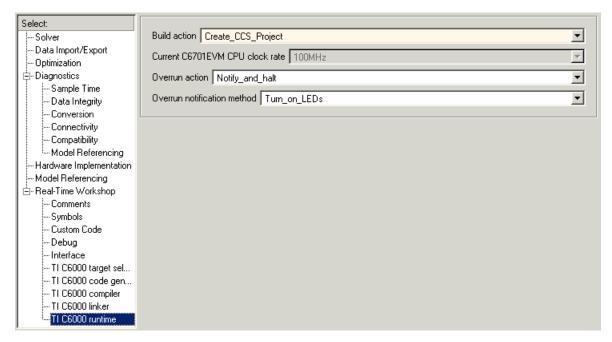

| Creating Code Composer Studio<br>Projects Without Building (p. 2-126)                          | You have the option of generating code into a Code Composer Studio project, rather than to hardware. This section introduces the Generate_CCS_project selection in the Real-Time Workshop build options. |

|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Targeting Custom Hardware (p. 2-128)                                                           | Discusses how you target processors on boards that are not supported boards. We call these boards custom targets.                                                                                        |

| Using Embedded Target for TI C6000<br>DSP with Real-Time Workshop<br>Embedded Coder (p. 2-132) | Provides details about using Embedded Target for TI C6000 DSP with your Real-Time Workshop Embedded Coder software and embedded real-time target.                                                        |

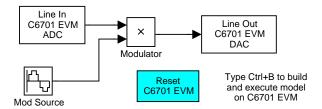

The Embedded Target for the TI TMS320C6000 DSP Platform lets you use Real-Time Workshop to generate a C language real-time implementation of your Simulink model. You can compile, link, download, and execute the generated code on the Texas Instruments (TI) C6701 Evaluation Module (C6701 EVM) and C6711 DSP Starter Kit (DSK). In combination with the supported boards (refer to "Supported Hardware For Targeting" on page A-2), your Embedded Target for TI C6000 DSP software is the ideal resource for rapid prototyping and developing embedded systems applications for the TI C6701 and C6711 digital signal processors. The Embedded Target for TI C6000 DSP software focuses on developing real-time digital signal processing (DSP) applications for C6000 hardware. Additional hardware that we support is listed in "Reference — Supported Hardware" on page A-1.

Although the tutorials in this chapter focus on the C6701 EVM and the C6711 DSK, the techniques and processes apply to any supported hardware, with minor adjustments for the processor involved.

This chapter describes how to use the Embedded Target for TI C6000 DSP to create and execute applications on Texas Instruments C6000 development boards. To use the targeting software, you should be familiar with using Simulink to create models and with the basic concepts of Real-time Workshop automatic code generation. To read more about Real-Time Workshop, refer to your Real-Time Workshop documentation.

#### **About the Tutorials**

In most cases, this chapter deals with either the C6701 EVM or the C6711 DSK targets. Fortunately, all members of the C6000 family of processors that we support work in a manner similar to the C6701 EVM and C6711 DSK. While you review the contents of this chapter, and follow the tutorials, recall that the concepts and techniques or development processes apply, with a few small adjustments, to all supported C6000 processors and boards.

# TI C6000 and Code Composer Studio IDE

Texas Instruments (TI) markets a complete set of software tools to use when you develop applications for your C6000 hardware boards. This section provides a brief example of how the Embedded Target for TI C6000 DSP uses Code Composer Studio $^{\text{TM}}$  (CCS) Integrated Development Environment (IDE) with the Real-Time Workshop and the C6000lib blockset.

Executing code generated from Real-Time Workshop on a particular target in real time requires that Real-Time Workshop generate target code that is tailored to the specific hardware target. Target-specific code includes I/O device drivers and an interrupt service routine (ISR). Since these device drivers and ISRs are specific to particular hardware targets, you must ensure that the target-specific components are compatible with the target hardware. To allow you to build an executable, TI C6000 uses the MATLAB links to invoke the code building process from within CCS. Once you download your executable to your target and run it, the code runs wholly on the target; you can access the running process only from the CCS debugging tools or across a link for CCS or Real-Time Data Exchange (RTDX). Otherwise the running process is not accessible.

Used in combination with your Embedded Target for TI C6000 DSP and Real-Time Workshop, TI products provide an integrated development environment that, once installed, needs no additional coding.

### **Supported Boards and Simulators**

Using the C6000 target provided by the Embedded Target for TI C6000 DSP, you can generate code to run on a range of boards, both evaluation modules and DSP starter kits.

Refer to "Reference — Supported Hardware" for the latest information about the hardware supported by the Embedded Target for TI C6000 DSP.

#### **About Simulators**

CCS offers many simulators for the C6701 and C6711 digital signal processors, and other C6000 processors in the CCS Setup utility. Much of your model and algorithm development efforts work with the simulators, such as code generation. And, since the Embedded Target for TI C6000 DSP provides a software-based scheduler, your models and generated code run on the simulators just as they do on your hardware. You can use the RTDX links with

the simulators as well. For more information about the simulators in CCS, refer to your CCS online help system.

When you set up a simulator, you must match the processor on your target exactly to simulate your target hardware. If you plan to target C6701 EVM boards, your simulator must contain a C6701 processor, not just a C6xxx simulator. Simulators must match the target processor because the codecs on the board are not the same and the simulator needs to identify the correct codec. Correctly matching your simulator to your hardware ensures that the memory maps and registers match those of your intended target signal processor.

#### **Using a Simulator**

You can use the simulator alone to develop projects with Embedded Target for TI C6000 DSP. The simulator can generate and handle timer interrupts properly to enable your generated code to run.

There is one manual step you need to do to use the simulator. After you generate code from a model to a CCS project, you must modify the project by setting the **RTDX Mode** in CCS to Simulator.

In addition, you must substitute the file rtdxsim.lib instead of the default rtdx.lib library file in the project. Accomplish this project file modification by navigating to the **Include Libraries** option:

#### **Build Options -> Linker -> Basic**

and replacing the file as needed in the Include Libraries option.

After you make this file substitution, you cannot use the Line In and Line Out ADC block options or any other target-specific board-level blocks. You can substitute any discrete-time sources and sinks from Simulink, Signal Processing Blockset, or other blockset. When there are no codec blocks (ADC or DAC blocks) in your model, the Embedded Target for TI C6000 DSP configures an on-chip timer to trigger the system at the appropriate sample time. As a result, whatever happens in the model is completely up to you, the user, as long as you provide the discrete sample time.

#### Using RTDX with a Simulator

If you are using DSP/BIOS in your project, you configure RTDX by opening the DSP/BIOS Config properties in the project tree, opening the project .cdb file,

and navigating to Input/Output. In the Input/Output properties you set the **RTDX mode** to Simulator.

If your project is not using DSP/BIOS, you only have to change the RTDX mode when you are using RTDX blocks in your model. Otherwise, RTDX is not needed.

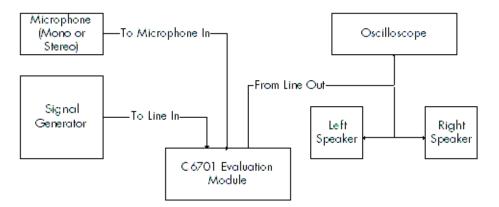

### Typical Hardware Setup for Developing Models

The next figure presents a block diagram of the typical setup for the inputs and output for the C6701 EVM. For the C6711 DSK, the typical layout is similar except the board accepts only monaural input from a microphone.

#### Block Diagram of Typical Inputs and Outputs to the C6701 EVM

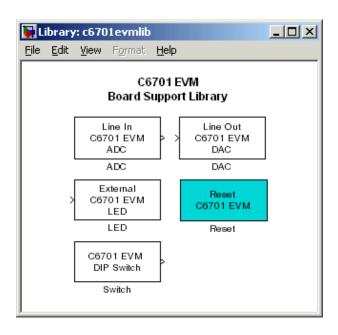

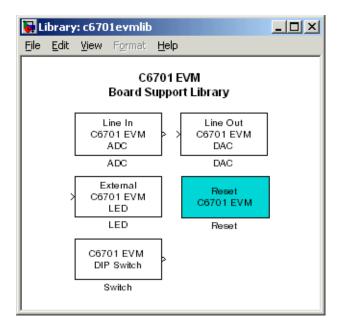

After you have installed one or more of the supported development boards shown in "Reference — Supported Hardware" on page A-1, start MATLAB. At the MATLAB command prompt, type c60001ib. This opens a Simulink blockset named C6000lib that includes libraries that contain blocks predefined for C6000 input and output devices:

- C6701 EVM Board Support blocks

- C6701 EVM ADC—configures the analog to digital converter

- C6701 EVM DAC—configures the digital to analog converter

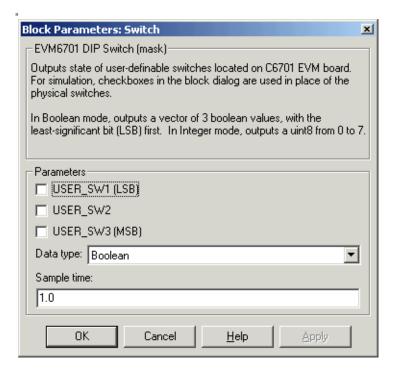

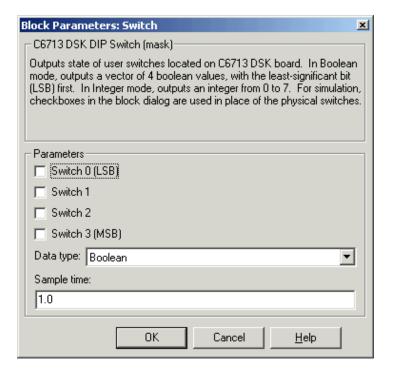

- C6701 EVM DIP Switch—simulates or reads the user-defined DIP switches on the C6701 EVM

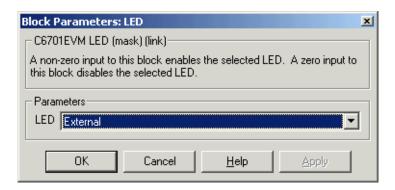

- C6701 EVM LED—controls the user status light emitting diodes (LED) on the C6701 EVM

- C6701 EVM Reset—resets the current C6701 EVM

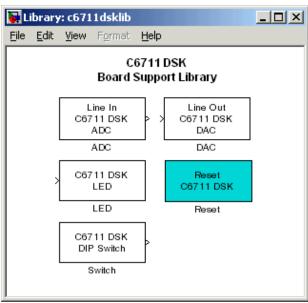

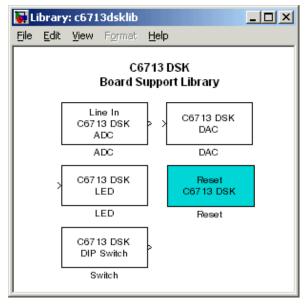

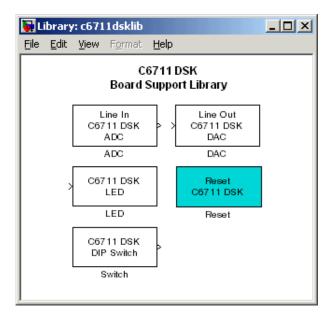

- C6711 DSK Board Support blocks

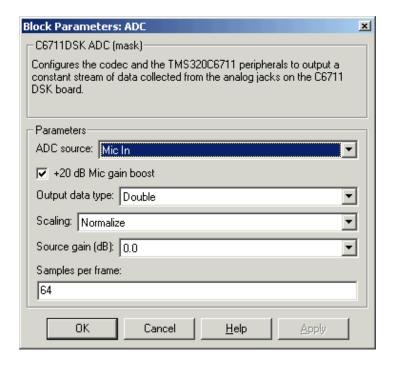

- C6711 DSK ADC—configures the analog to digital converter

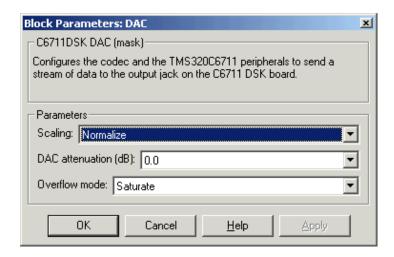

- C6711 DSK DAC—configures the digital to analog converter

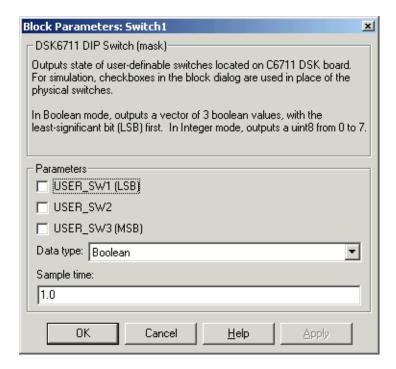

- C6711 DSK DIP Switch—simulates or reads the user-defined DIP switches on the C6711 DSK

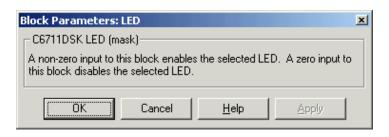

- C6711 DSK LED—controls the three user status light emitting diodes (LED) on the C6711 DSK

- C6711 DSK Reset—resets the current C6711 DSK

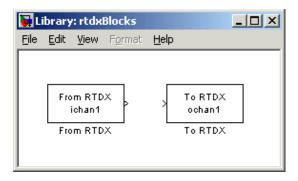

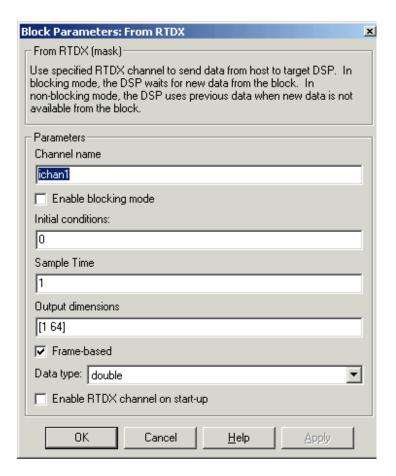

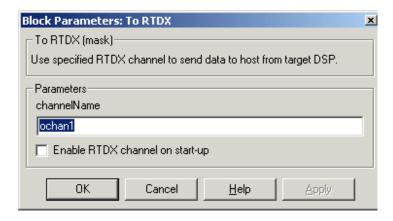

- RTDX Instrumentation

- From RTDX—adds an RTDX input channel to the code generated from your model. When you run the model on your target, the block code imports data from your host over an RTDX channel to your running process.

- To RTDX—adds an RTDX output channel to the code generated from your model. When you run the model on your target, the block code exports data to your host over an RTDX channel from your running process.

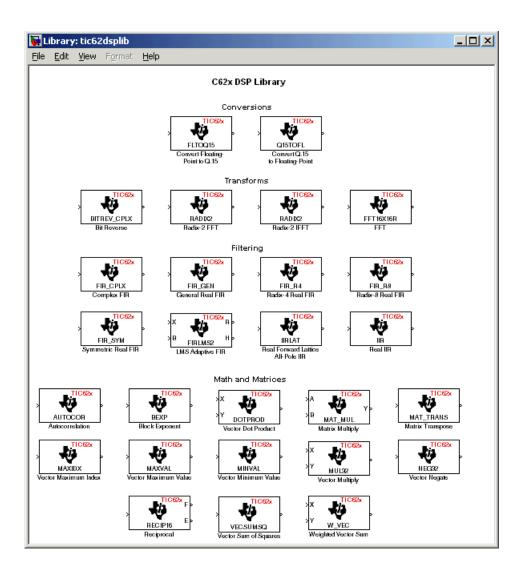

- C62x DSP Library

- Provides fixed-point blocks for models that use fixed-point mathematics and algorithms.

- C64x DSP Library

- Provides fixed-point blocks for models that run on C64x processors.

- C6416 DSK Board Support

- Blocks to configure the peripherals on the C6416 DSK.

- C6713 DSK Board Support

- Blocks to configure the peripherals on the C6713 DSK.

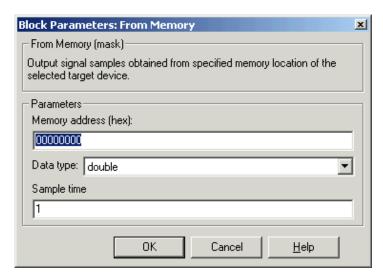

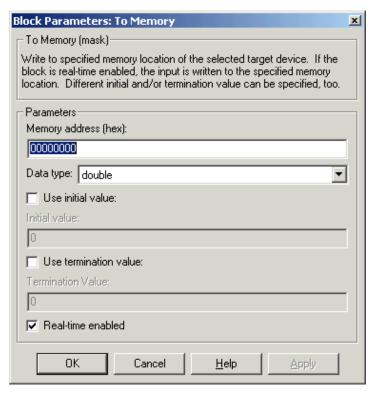

- C6000 DSP Core Support

- Blocks that provide data transfer to and from memory on all C6000 hardware.

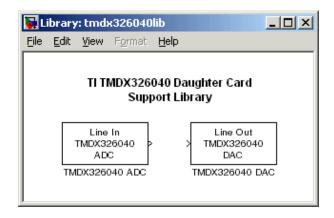

- TMDX326040 Daughtercard Support

- Blocks that configure the peripherals associated with the daughtercard.

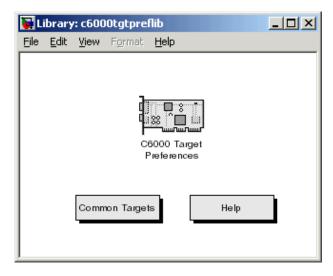

- Target Preferences

- Icon blocks that allow you a shortcut to setting the target type for a model These blocks are associated with your boards and hardware. As needed, add the devices to your model. If you choose not to include either an ADC or DAC block in your model, Embedded Target for TI C6000 DSP provides a timer that produces the interrupts required for timing and running your model, either on your hardware target or on a simulator.

In addition to the blocks for specific boards, the C6000lib blockset includes the library RTDX Instrumentation that contains RTDX input and output blocks that apply to all C6000 development boards and the C6000 DSP Core support library that contain blocks that let you transfer data to and from memory on any C6000-based target. Like the RTDX blocks, the core support blocks are not hardware dependent.

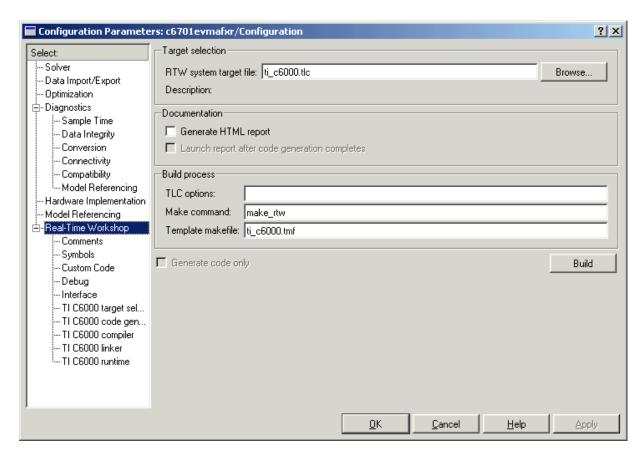

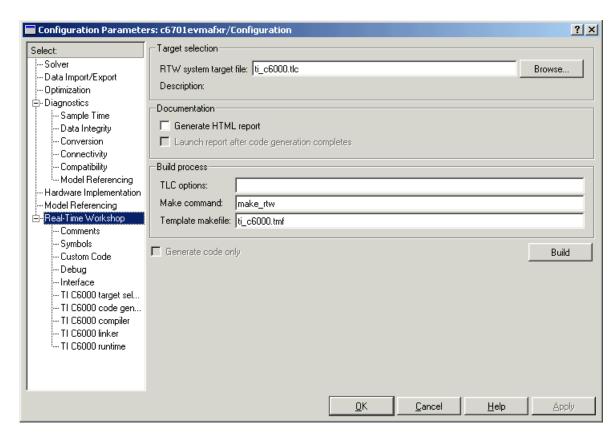

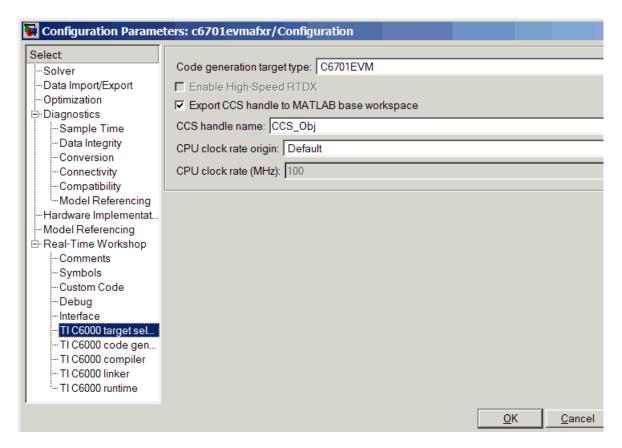

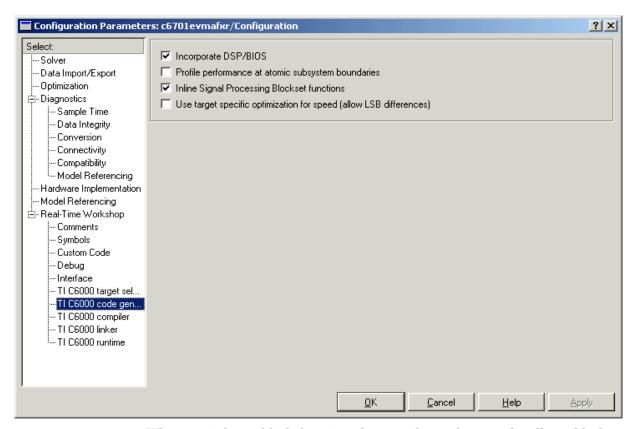

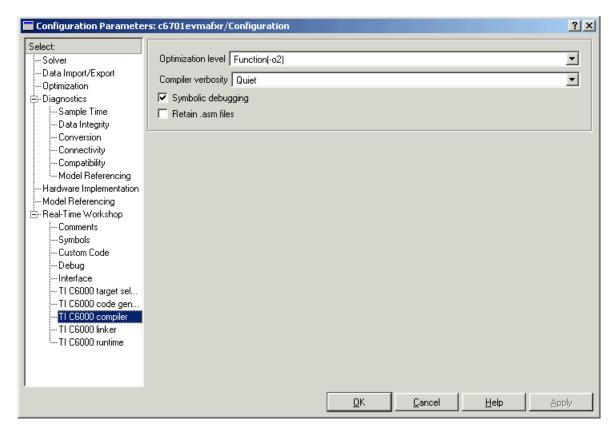

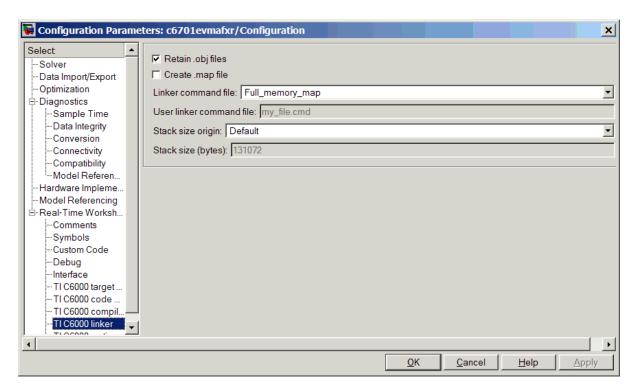

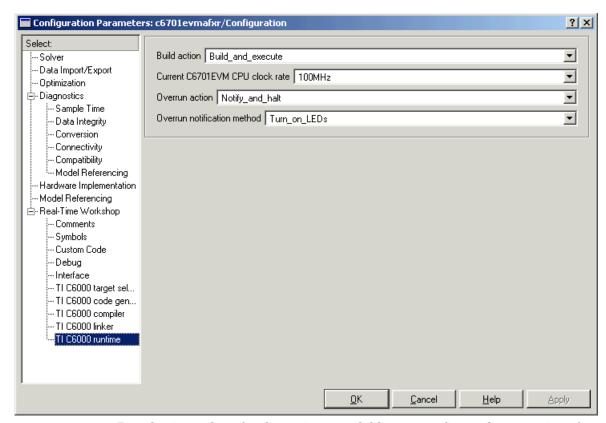

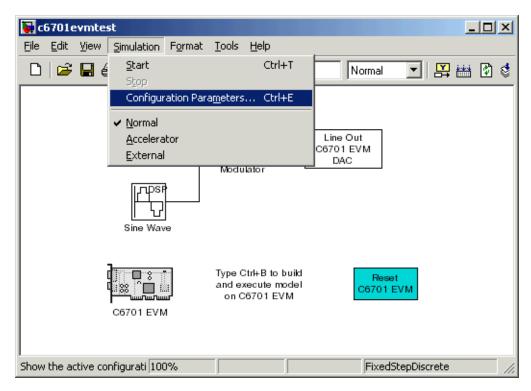

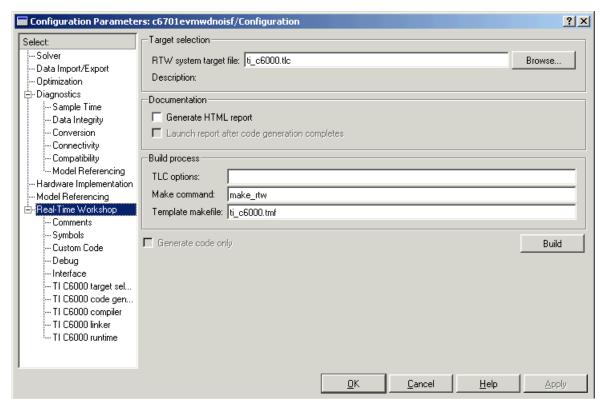

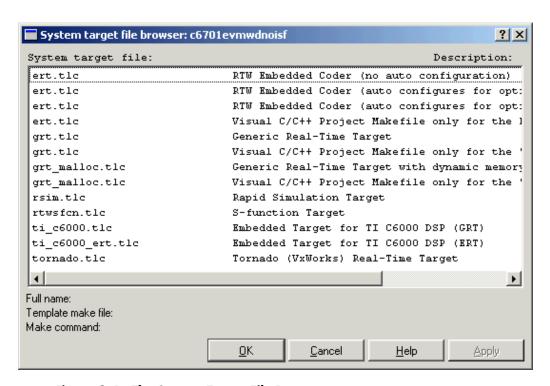

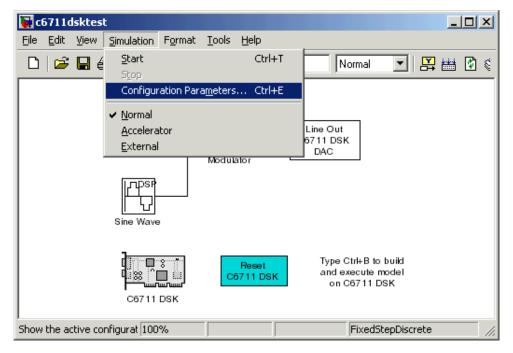

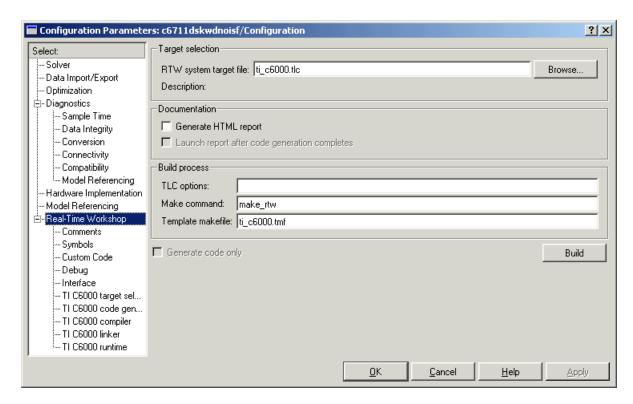

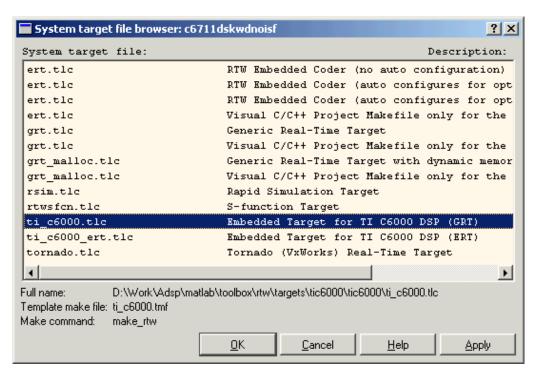

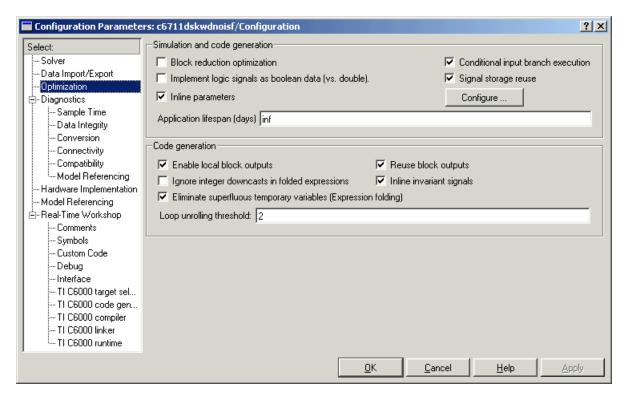

With your model open, select **Configuration Parameters** from the **Simulink** option to open the **Configuration Parameters** dialog box. In the **Select** tree, click Real-Time Workshop. You must specify the appropriate versions of the system target file and template makefile. For the C6701 EVM or the C6711 DSK, in the Real-Time Workshop pane of the dialog, specify

ti c6000.tlc

to select the correct target file in RTW system target file. Or click **Browse** and select ti\_c6000.tlc from the list of targets, or whichever target best matches your hardware.

With this configuration, you can generate a real-time executable and download it to the TI development boards. You do this by clicking **Build** on the Real-Time Workshop pane. Real-Time Workshop automatically generates C code and inserts the I/O device drivers as specified by the ADC and DAC blocks in your block diagram, if any. These device drivers are inserted in the generated C code as inlined S-functions. Inlined S-functions offer speed advantages and simplify the generated code. For more information about inlining S-functions, refer to your target language compiler documentation. For a complete discussion of S-functions, refer to your documentation about writing S-functions.

During the same build operation, the template makefile and block parameter dialog entries get combined to form the target makefile for your TI C6000 board. Your makefile invokes the TI cross-compiler to build an executable file. If you selected the Build and execute build action, the executable file is automatically downloaded via the peripheral component interface (PCI) bus to

your C6701 evaluation module, or over the parallel port to your C6711 DSK. After downloading the executable file to the target, the build process runs the file on the board's DSP.

# **Using the C6000lib Blockset**

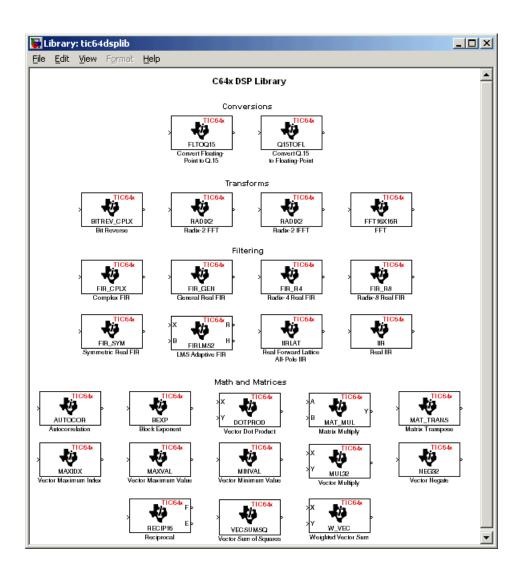

The Embedded Target for TI C6000 DSP blockset C6000lib comprises block libraries that contain blocks designed for targeting specific boards or using RTDX. The libraries are

- C6701 EVM Board Support—blocks to configure the codec and LEDs on the C6701 EVM

- C6711 DSK Board Support—blocks to configure the codec and LEDs on the C6711 DSK

- RTDX Instrumentation—blocks for adding RTDX communications channels to Simulink models

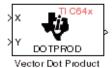

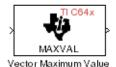

- TI C62x DSPLIB—fixed-point blocks for developing models for fixed-point targets

- C64x DSP Library—provides fixed-point blocks for models that run on C64x processors.

- C6416 DSK Board Support—blocks to configure the peripherals on the C6416 DSK.

- C6713 DSK Board Support—blocks to configure the peripherals on the C6713 DSK.

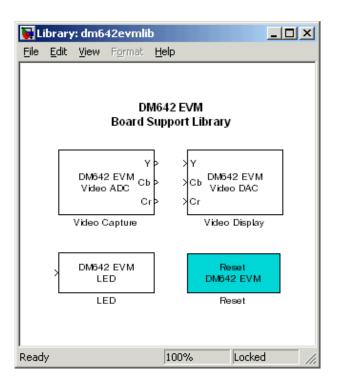

- DM642 EVM Board Support—blocks to configure the video peripheral devices and LEDs on the DM642 EVM

- C6000 DSP Core Support—blocks that provide data transfer to and from memory on all C6000 hardware.

- TMDX326040 Daughtercard Support—blocks that configure the peripherals associated with the daughtercard.

- Target Preferences—icon blocks that allow you a shortcut to setting the target type for a model.

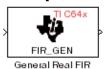

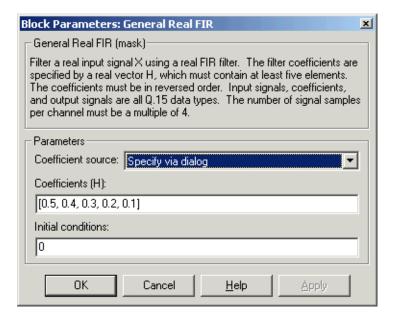

Each block library appears in one of the next figures. The sections after the figures review the configuration options for blocks in the EVM and DSK block libraries. For more information about the RTDX blocks, refer to "Constructing Link Objects" in your Link for Code Composer Studio documentation.

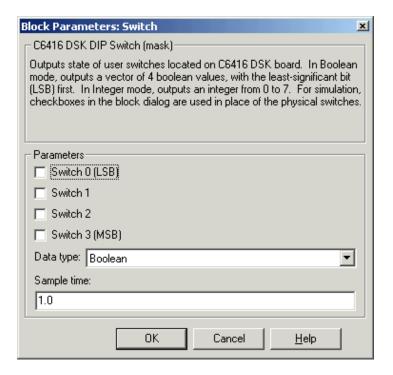

Each board-based block library contains a version of each of these blocks:

ADC block

- DAC block

- DIP Switch block (optional, refer to the reference page for the DIP Switch block for your target)

- LED block

- Reset block

Similarities in the C6000 boards result in the ADC, DAC, DIP Switch, LED, and Reset blocks for the C6000-based boards being almost identical. Each section about a block, such as the ADC block, presents all possible options for the block, noting when an option applies only to a board-specific version of the ADC block. For example, the **Codec data format** option for ADC blocks applies only to the C6701 EVM ADC.

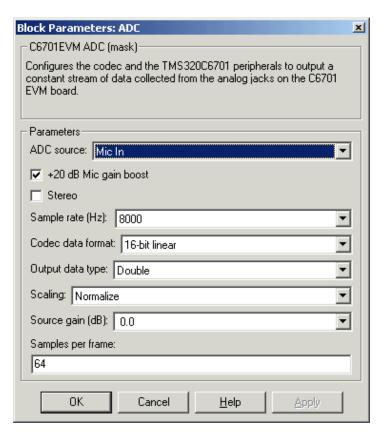

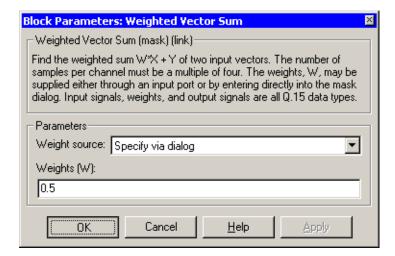

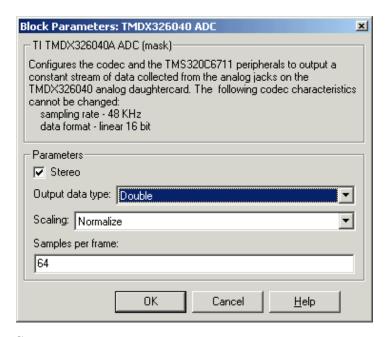

#### **Configuring ADC Blocks**

To drive and test your DSP application on a C6701 EVM or C6711 DSK, you use signals from external sources, such as signal generators, audio equipment, or microphones. In some cases, you may generate your input data in code using Simulink blocks in your model or from a source block, such as a signal generator; configuring the ADC block remains the same.

The ADC and DAC blocks provide physical pathways from and to external sources and displays. They behave like source and sink blocks. They differ from sources and sinks in that they exchange data with external devices through analog input and output connectors, not the MATLAB workspace, and they work only for the C6000 boards.

You add ADC blocks to a model in the same way that you add other Signal Processing Blockset blocks, or Simulink blocks. You can add at most one ADC block to a model. When you add C6000 blocks to your Simulink model, you set parameters that determine how each block handles data.

Adding the ADC block to your Simulink model enables the codec on the target to accept input from your external source. By connecting your source to the LINE IN connector on the board mounting bracket, you introduce signals to the board. Your ADC block defines the signal format the codec uses to sample, digitize, and send signals to the digital signal processor. When you build your Simulink model, the build process includes the software to implement the ADC-defined codec operation into the code downloaded to the board.

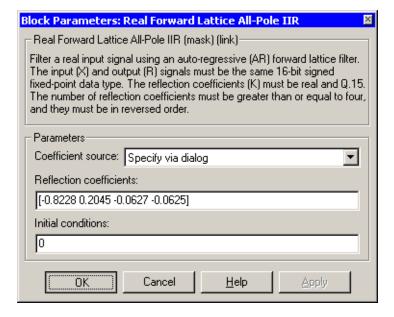

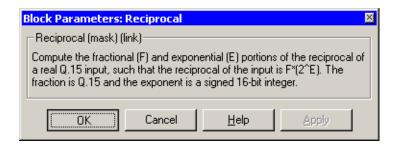

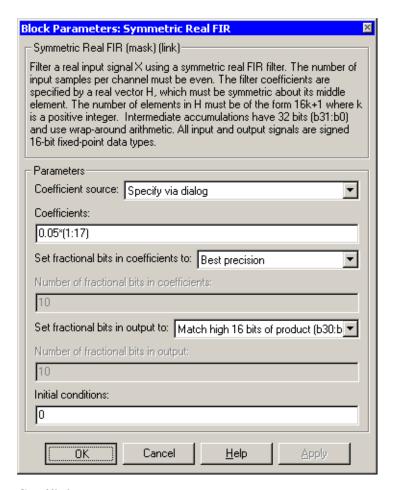

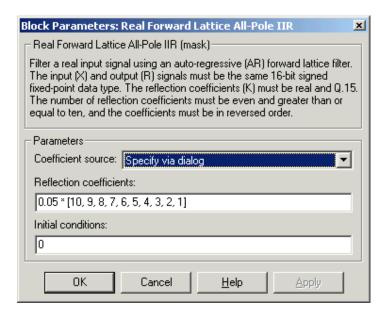

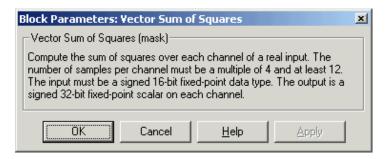

Configuring an ADC block includes setting as many as nine parameters on the **Block Parameters** dialog.

Choosing and setting these parameters are covered in the following sections. To help you select the settings, this section provides some guidelines for common DSP uses and applications for each parameter. While the examples are not exhaustive, the suggestions may help you select settings that work well for your application.

Most of the configuration options for the block affect the codec. However, the **Output data type**, **Samples per frame**, and **Scaling** options relate to the model you are using in Simulink, the signal processor on the board, or direct memory access (DMA) on the board. In the following table, you find each option listed with the target board hardware affected.

| Option                                    | Affected Hardware |

|-------------------------------------------|-------------------|

| ADC Source                                | Codec             |

| Codec data format (C6701<br>EVM ADC only) | Codec             |

| Mic                                       | Codec             |

| Option                                | Affected Hardware                    |

|---------------------------------------|--------------------------------------|

| Output data type                      | TMS320C6xxx digital signal processor |

| Sample rate (Hz) (C6701 EVM ADC only) | Codec                                |

| Samples per frame                     | Direct memory access functions       |

| Scaling                               | TMS320C6xxx digital signal processor |

| Source gain (dB)                      | Codec                                |

| Stereo (C6701 EVM ADC only)           | Codec                                |

#### Selecting the ADC Source

When you set up your target to accept input for your model, you tell the hardware where the input to the codec comes from. Selecting **Line in** and **Mic in** on the C6701 EVM corresponds to the two different input connectors on the board, with different input signal levels expected. On the DSK, the **Line in** and **Mic in** options use the same connector, but generate different signal levels to the codec. Both boards include the **Loopback** option that feeds the output from the DAC back to the ADC input.

#### Choosing the Sample Rate (C6701 EVM ADC Block Only)

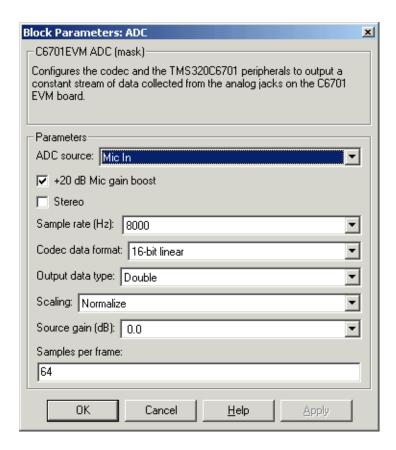

To open the **Block Parameters** dialog, right-click the C6701 EVM ADC block in your Simulink model and select **Block Parameters** from the context menu. You see the dialog presented in Figure 2-1, Block Parameters for C6701 EVM ADC Dialog.

Figure 2-1: Block Parameters for C6701 EVM ADC Dialog

Select your sample rate from the list. 5521 Hz is the lowest rate and 48000 Hz is the highest. You cannot set a sample rate that is not on the list. The available rates are derived from the clocks on the codec and cannot be changed.

The C6711 DSK uses a fixed sample rate of 8 KHz.

For many applications, your sample rate should reflect the standards for the industry. For example, if you are developing a professional audio application, working with digital audio tape (DAT) processes, or developing applications for high fidelity audio use, consider using 48000 Hz sampling rate in your model. In addition, choose double-precision, fixed-point arithmetic format when you select the **Codec data format**.

For applications used by CD players and sound cards in personal computers, the standard sampling rate is 44.1 KHz, and some of the lower rates such as 22.05 or 16 KHz. Moving Picture Expert Group (MPEG) audio applications often select a 32 KHz sampling rate.

When you are developing an application for speech, telephony, or "toll quality" speech processing, the 8 KHz sampling rate, paired with one of the 8-bit data formats that use a compressed format such as A-law, best matches current standards.

#### Choosing the Codec Data Format (C6701 EVM ADC Only)

When the codec performs A/D conversion, the output data format is partly determined by the setting for **Codec data format** in the **Block Parameters** dialog. **Codec data format** offers five choices:

- 16-bit linear—the standard method of representing 16-bit digital audio. Provides 96 dB theoretical dynamic range and best fits the standard for compact disk audio players. -32768 represents the maximum negative analog amplitude and 32767 represents the maximum positive analog amplitude.

- 8-bit linear—commonly used in the PC industry. Provides 48 dB theoretical dynamic range. 00 represents the maximum negative analog amplitude and 255 represents the maximum positive analog amplitude.

- 8-bit A law—used in the telephone industry most frequently. A-law is the European standard; μ-law is the standard in Japan and the United States. Uses a nonlinear companding transfer function to digitize analog input to provide 64 dB or 72 dB maximum dynamic range.

- 8-bit μ law—used in the telephone industry most frequently. μ-law is the standard in Japan and the United States; A-law is the European standard. Uses a nonlinear companding transfer function to digitize analog input to provide 64 or 72 dB maximum dynamic range.

- 4-bit IMA ADPCM—voice digitization scheme that uses a lower bit rate than pulse code modulation (PCM). ADPCM records only the difference between samples, and adjusts the coding scale dynamically to accommodate large and small differences. This scheme is simple to implement, but can introduce significant noise. The G.721 method uses 32Kbps per voice channel, as compared to standard telephony's 64Kbps using PCM. Using ADPCM

instead of PCM is imperceptible to humans—but it can significantly reduce the throughput required by higher-speed modems and fax transmissions.

You will probably use 16-bit linear codec data format when you begin developing your model. If you do not care about, or do not expect, negative data values, as would be the case where you are measuring a voltage that varies from 0 volts to 5 volts, you could use 8-bit unsigned math. If appropriate for your application, choose one of the compression data formats for your model.

#### Selecting the Data Type

You must select the data type when you include the ADC block in your DSP simulation. The data type you use in the simulation is likely not to be the one you use when you build and download the application to the target. Your choice of data type depends on a number of factors related to how the application runs on the target DSP and what limitations apply. Four factors can influence your choice:

- Processing time—how long does each iteration of your process take? Can the DSP process the data quickly enough to meet your needs?

- Power used—how much power does the application require? Doing lots of multiply and divide operations uses more power and generates more heat than add operations.

- Memory required—how does your application use memory and how much does it need?

- Does accuracy matter—do you need the accuracy provided by double-precision arithmetic or is fixed-point or integer acceptable?

When you have developed and tested your signal processing application in Simulink, you are ready to use Real-Time Workshop and your Embedded Target for TI C6000 DSP to build and download your model to the C6701 EVM or C6711 DSK. Your Simulink model should represent a general purpose implementation of your application, without specific features that depend on the target DSP. For instance, use floating-point arithmetic and single- or double-precision format to develop your simulation. Select DSP target-specific data and format requirements when you prepare your model for the board.

**Note** If you use fixed-point arithmetic in your processing algorithm or application on the C6701 EVM or C6711 DSK, verify that the blocks in your Simulink model will work with the processor in integer mode.

Blocks in the C62 DSPLIB library are designed specifically for fixed-point models.

To ease model development on the target, start by selecting floating-point data format when you build and download your application to the board. You could choose either single-precision or double-precision at this time to ensure that your model runs on the target processor. Often, normalized floating-point arithmetic is the best choice during development. As you tune your model for your target processor, consider whether such factors such as calculation time and memory use are important in your application environment. If time is a critical parameter, use either less precise math, such as single precision instead of double, or switch from floating point to fixed point or integer. Making these changes both speeds up your process and reduces the memory and power your processor consumes to complete its calculations.

For accuracy without regards to time, use floating-point arithmetic.

#### Selecting the Scaling

Both the single-precision and double-precision data types are available as floating point or normalized values. During development, it is a good idea to start with normalized values to relieve you from worrying about overflows and underflows in the calculations performed in the algorithm. When you are happy that the process is under control, change the data type to the one you need for the deployed executable code.

Selecting a floating-point data type can reduce your algorithm processing overhead slightly.

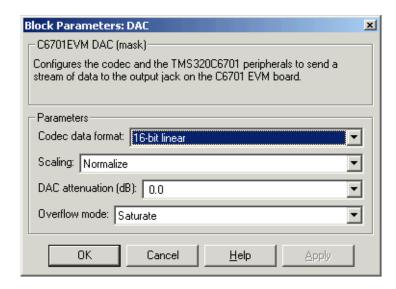

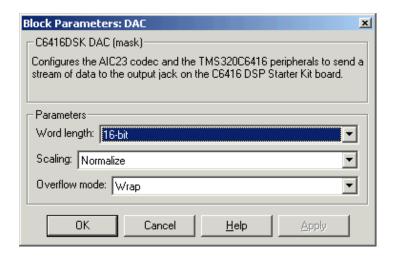

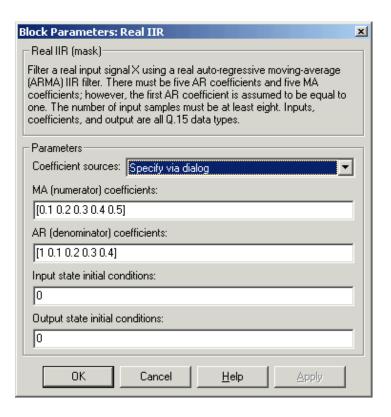

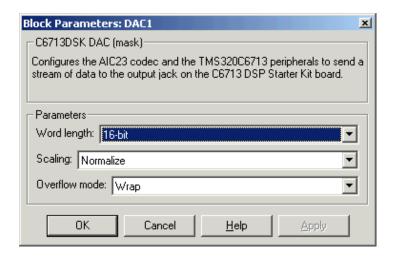

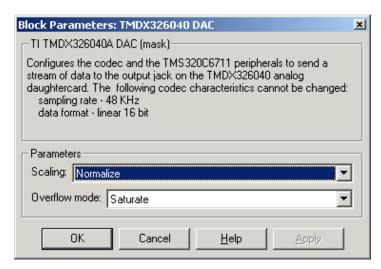

## **Configuring DAC Blocks**

In most cases, DAC blocks inherit attributes from the ADC block in the model, or from the previous nonvirtual block. You must select **Codec data format**, **Scaling**, and **Overflow mode** when you use a C6701 EVM DAC block in your

model. In addition, you can choose to use the overrun indicator function provided in the Embedded Target for TI C6000 DSP.

Two of the configuration options for the block affect the codec. The remaining options relate to the model you are using in Simulink and the signal processor on the board. In the following table, you find each option listed with the hardware affected.

| Option                                    | Affected Hardware        |

|-------------------------------------------|--------------------------|

| Codec data format<br>(C6701 EVM DAC only) | Codec                    |

| DAC attenuation                           | Codec                    |

| Overflow mode                             | Digital Signal Processor |

| Scaling                                   | Digital Signal Processor |

When you double-click the C6701 EVM DAC block, you see the dialog shown here.

#### Choosing the Codec Data Format (C6701 EVM DAC Block Only)

The **Codec data format** for the C6701 EVM DAC block must be the same as the **Codec data format** for the C6701 EVM ADC block, if you use one in your model. C6711 DSK codec blocks do not offer the **Codec Data Format** option.

#### Selecting the Scaling

Select the scaling that best suits your model and your output device. For most applications, choose the scaling to match the setting of the ADC block if your model uses it.

Scaling defines the range of the input values from the codec. Independent of your setting for **Scaling**, signal values are stored as floating-point data. In Normalize mode, the signal ranges from -1 to 1 at the output of the ADC block. When you select Integer value for the scaling, the signal ranges between the minimum and maximum values representable by the number of bits specified by **Codec data format**.

#### Selecting the Overflow Mode

Models running on the target can encounter situations where calculations exceed the range represented by the data type. The **Overflow mode** option on the **DAC** dialog lets you select how the block responds to overflow conditions. Select one of the following settings:

- Saturate—arithmetic results that fall outside the representable range of the selected data type are limited to the largest or smallest values. Saturated values are set to the nearest value that the data type can represent, either the largest representable value in the case of arithmetic overflow or the smallest representable value in the case of arithmetic underflow.

- Before input data reaches the codec, the Embedded Target for TI C6000 DSP uses an efficient linear assembly algorithm to determine whether the input values exceed the representable range of your selected data type. When input values exceed the range of the data type, the saturation algorithm clips the input to the nearest representable value and passes the clipped, or *saturated*, value to the codec.

- Wrap—arithmetic results that fall outside the numeric range of the selected data type are wrapped into the range of the data type. The wrapping algorithm uses modular arithmetic relative to the largest or smallest representable number to determine the value of the result after wrapping.

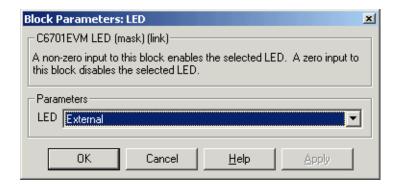

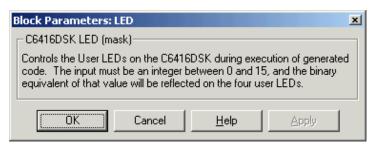

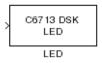

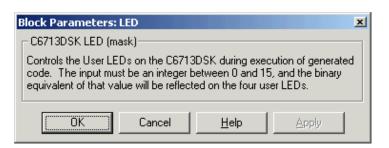

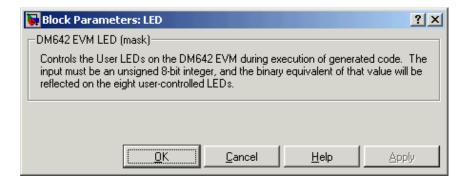

#### **Configuring LED Blocks**

You use the LEDs on the evaluation module as indicators for your process. For example, you might use an LED to indicate that your algorithm has completed a specified calculation or reached a particular point in the processing.

To use an LED as an indicator, add an LED block to your model, and send a nonzero signal to the block to light the specified LED—either internal or external. Any nonzero scalar sent to the LED block lights the LED and keeps it lit until the block receives a scalar with zero value. The zero value scalar turns off the selected LED.

Since the C6701 EVM provides two LEDs, you can use two C6701 EVM LED blocks—one for each user status LED on the board. Although the C6711 DSK offers three user-defined LEDs, the C6711 DSK LED block treats all three as one LED, enabling them as a group. For this reason you can include only one C6711 DSK LED block in a model.

#### Select the Target LED (C6701 EVM LED Block Only)

Double-clicking the C6701 EVM LED block opens the dialog shown here.

When you add an C6701 EVM LED block to your model, you use the **LED** list to select which LED the block controls—internal or external. Select External from the list to have the C6701 EVM LED block trigger the LED located on the C6701 EVM mounting bracket at the back of your PC. To trigger the internal LED located on the C6701 EVM board internally, select Internal for the **LED** setting.

## **Using the Overrun Indicator Feature**

When your digital signal process application cannot complete the calculations and data manipulations required to yield a result before the available clock cycles expire, your model can generate unreliable data. Failing to complete an algorithm is called overrunning, and is one of the most important errors to identify and eliminate in digital signal processing design and implementation.

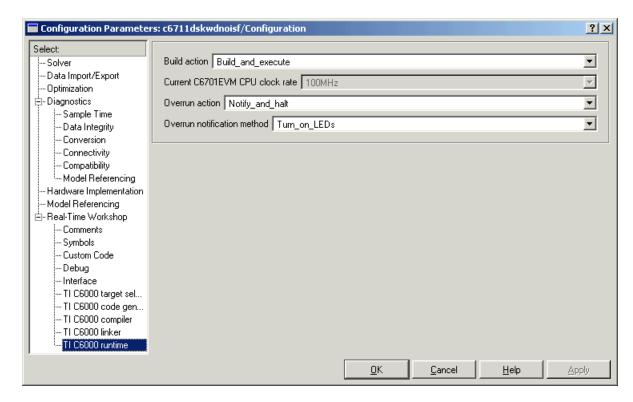

The Embedded Target for TI C6000 DSP provides a pair of overrun indicator options—Overrun action and Overrun notification method—that you use to determine what happens when your application overruns and how or if to notify you when your process runs out of processing time before it completes its tasks. To signal that your algorithm has overrun its limits, the Embedded Target for TI C6000 DSP can turn on the external LED on your C6701 EVM and leave it on until you reset the evaluation module. The overrun feature can also print a message that the overrun occurred to the standard output device—stdout (or the message log if your application uses DSP/BIOS). One more option lets you both light the LED and print a message.

#### Limitations on the Overrun Indicator

In two cases, the overrun indicator does not work:

- In multirate systems where the rate in the process is not the same as the base clock rate for your model. In this case, the timer/scheduler in the Embedded Target for TI C6000 DSP provides the interrupts for setting the model rate and you cannot use the overrun indicator.

- In models that do not include ADC or DAC blocks. In this case, the timer/scheduler provides the software interrupts that drive model processing.

To detect overrun conditions, the generated C code sets and checks a persistent flag during each iteration of the direct memory access (DMA) interrupt service routine.

To indicate an overrun condition on the C6711 DSK, the software turns on all three user-defined LEDs on the board.

**Note** The **Overrun notification method** selections that turn on the LEDs use the external LED or user-defined LEDs to signal model conditions. If you are using the overrun indicator, consider not using an LED block to trigger the external LED on the C6701 EVM, or the user LEDs on the C6711 DSK until you stop monitoring your process for overrun conditions.

To enable the overrun indicator, choose one of three options for **Overrun action** to determine how to respond to an overrun condition in your model:

- None—your model does not respond to overrun conditions during processing.

- Notify\_and\_continue—when your model runs out of clock cycles before

completing enough of the processing algorithm, the overrun indicator

executes the option you chose for Overrun notification method. The model

continues to run without pause.

- Notify\_and\_halt—when your algorithm runs out of clock cycles before

completing the required calculations and manipulations, the model stops

executing and notifies you about the overrun using the method you select for

the Overrun notification method.

Overrun notification method provides three ways to tell you when an overrun has occurred:

- Print\_message—print a message to stdout, or the message log when your application uses DSP/BIOS

- Turn\_on\_LEDs—illuminate the user LEDs on the target, either the external LED on the C6701 EVM or all of the user LEDs on the C6711 DSK

- $\bullet$  Print\_message\_and\_turn\_on\_LEDs— light the LEDs and print a message

## **Configuring Reset Blocks**

Each target library offers a block that performs a software reset of the appropriate board—a Reset block. While they are blocks, Resets do not require input; they do not provide output; and they do not need to be connected to any other block.

When you add a Reset block to a model window, it provides single-click access to resetting your board. Click on the block in your model and your target

processor returns to its original state, with the memory locations, registers, and other peripherals reset to their default values before you loaded or ran a program.

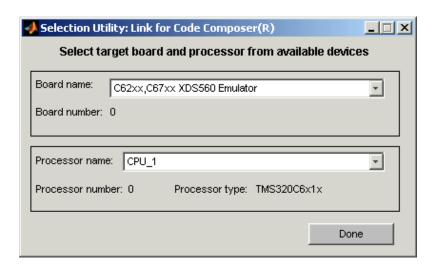

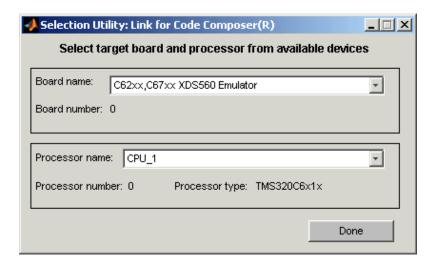

#### **Configuring Target Preferences Blocks**

One block is common to all C6000 targets—the Target Preferences block in the C6000 Target Preferences library. Adding one of these blocks to your model provides direct access from the model to the target **Selection Utility** dialog where you choose your target board and processor.

If you do not include a Target Preferences block in your model, or if the existing Target Preferences block indicates a target name which does not exist, Embedded Target for TI C6000 DSP places the new project into the CCS IDE window for board 0 as defined in the CCS Setup Utility. When you have more than one target configured for CCS, this default behavior may not put the project in the target you intend. Watch for error messages such as

File does not match the target type.

as an indication that the project may be in the wrong, or an unintended, target location.

Clicking this block opens the standard Selection Utility dialog shown here in one default configuration based on the existing defined targets.

#### **Board** name

Contains a list of all the boards defined in CCS. From the list of available board you select the one that matches your needs.

#### **Board number**

Reports the number of the board you select in Board name. Board number comes from the CCS Setup Utility you use to configure CCS targets. The number here is the number you assign or accept when define your target in the Setup Utility.

#### Processor name

Lists the processors available on the board you selected. In many cases, only one name appears because the board has only one processor. In the multiprocessor case, you select the processor by name from among the available processors on the board.

#### **Processor number**

Reports the number of the processor on the board you select in Board name. Processor number comes from the CCS Setup Utility you use to configure CCS targets. The number here is the number you assign or accept when define your target in the Setup Utility.

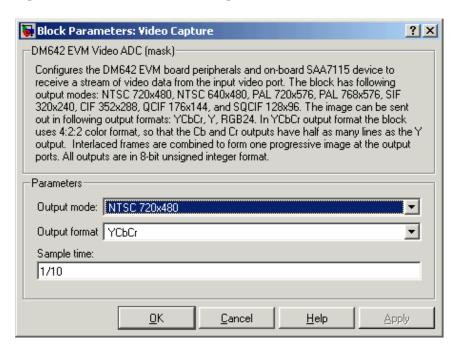

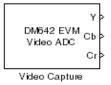

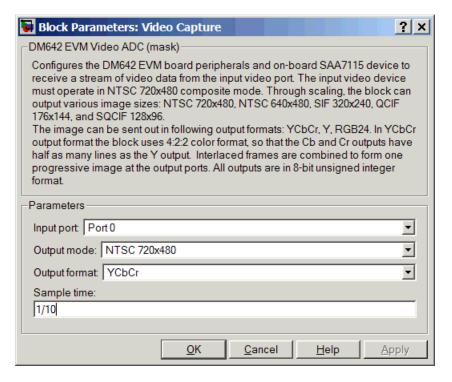

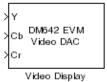

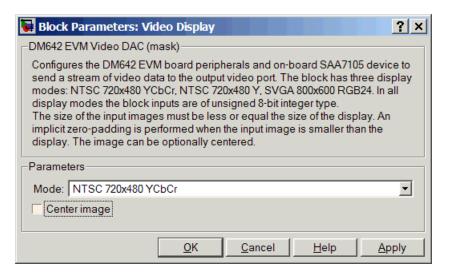

## Configuring DM642 EVM Video ADC and Video DAC Blocks

Preparing the Video ADC and Video DAC blocks for the DM642 EVM is quite different from configuring the ADC and DAC blocks for the other supported hardware. Rather than being just analog-to-digital converters, or digital-to-analog, the DM642 blocks allow you to capture and display video data. While conversion is a part of what they do, the configuration process sets up the video formats that the video capture block accepts and the video output block provides for display.

#### Configuring the Video ADC or Video Capture Block

To capture video from the video inputs on your DM642 EVM so you can use the video in your processing, add the DM642 Video ADC block to capture the video input. Options in the block let you set the output format and output mode of video that leaves the block for processing in your model. Setting the options

configures the peripherals on your board, and the SAA7115 video decoders to capture and reformat video for output.

From the available options in the dialog, you see that you do not need to configure the block for the type of video input. The block accepts whatever supported video you provide at the video input ports. Options in the dialog let you specify how to output the video from the block to downstream model elements.

| Option        | Affected Hardware       |

|---------------|-------------------------|

| Output mode   | SAA7115H video decoders |

| Output format | SAA7115H video decoders |

| Sample time   |                         |

#### Selecting the Output Mode

In the Video ADC dialog, the option Output mode sets the size in pixels and lines of the frames the block outputs, and the frame rate. Also how the data frames get assembled into images. By choosing a mode from the list, you tell the video decoder to take the input video stream and convert it to the mode/size you selected. Mode selection supports the following video standards, shown in the **Output mode** list.